## Conformal Step Coverage of Electron Beam-Assisted CVD of SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> Films

L. R. Thompson,\* L. Gobis, \*\* D. Bishop, J. J. Rocca, K. Emery, and G. J. Collins

Department of Electrical Engineering, Colorado State University, Fort Collins, Colorado 80523

We have recently reported electron beam assisted chemical vapor deposition (CVD) of silicon dioxide (SiO $_2$ ) and silicon nitride (Si $_3$ N $_4$ ) films at low (200°C) substrate temperatures (1,2,3). Herein, we examine the ability of the electron beam deposition technique to conformally cover patterned aluminum and polysilicon steps.

Conformal coverage of such uneven features by deposited dielectric layers without thin-ning and cusping is important in multilayer metal devices. Thinning of dielectric side-walls lowers interlayer breakdown voltages and cusping causes step coverage problems in subsequent metallization steps.

Details of the experimental arrangement and the electrical, physical and chemical properties of both  $\mathrm{SiO}_2$  and  $\mathrm{Si}_3\mathrm{N}_4$  films deposited using the electron beam assisted CVD technique have been presented elsewhere (1, 2, 3). Reactant gases used for the deposition of  $\mathrm{SiO}_2$  and  $\mathrm{Si}_3\mathrm{N}_4$  films include nitrous oxide and ammonia as respective oxygen and nitrogen donors. The silicon donor was 5% silane in nitrogen.

The deposition technique uses an electron beam to generate a spatially confined plasma reaction volume. To a first approximation the plasma region is a planar sheet with cross sectional area 1 x  $^25$  mm. Deposition occurs at rates up to 500 Å/min on a heated substrate (150-500°C) located directly beneath the planar region defined by the electron beam generated plasma.

To study the step coverage properties of the electron beam deposition technique aluminum was sputter deposited (8000Å thick) upon a thermal SiO<sub>2</sub> (1000Å thick) covered silicon wafer. The wafer was masked using conventional photolithography and wet chemically etched to achieve aluminum lines 10 to 20 µm wide. Separately a polysilicon layer (4000Å thick) was deposited over another thermal SiO<sub>2</sub> (1000Å thick) covered silicon wafer. The polysilicon

was also masked and standard dry processing techniques were used to achieve polysilicon lines 10 to 20  $\mu m$  wide.

${

m Si0}_2$  layers were then electron beam deposited on both aluminum and polysilicon patterned silicon wafers. The  ${

m Si0}_2$  films were deposited at a substrate temperature of 350°C, with a  ${

m N}_2{

m O}/{

m SiH}_4$  mass flow ratio of 20 and a chamber pressure of 0.3 Torr. The electron beam discharge current and voltage were 50 mA and 4 kV, respectively.

Separately  $\mathrm{Si}_3\mathrm{N}_4$  films were electron beam deposited at substrate temperatures of 350°C, with a  $\mathrm{NH}_3/\mathrm{SiH}_4$  mass flow ratio of 60 and a total chamber pressure of 0.35 Torr. The electron beam current and voltage were 25 mA and 4.2 kV, respectively.

After electron beam SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> deposition the silicon wafers were cleaved revealing the coverage over aluminum and polysilicon steps using a SEM. For the case of polysilicon steps the wafer was etched in a 1 M KOH solution in order to distinquish the polysilicon and SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub> interface while aluminum covered wafers were cleaved at 77 K to obtain sharp metal lines.

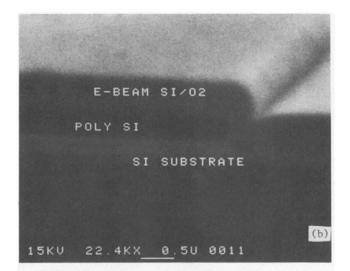

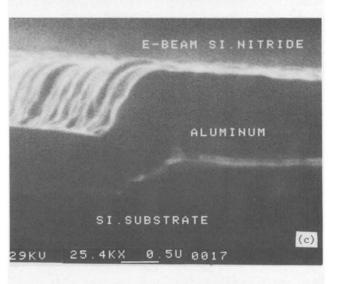

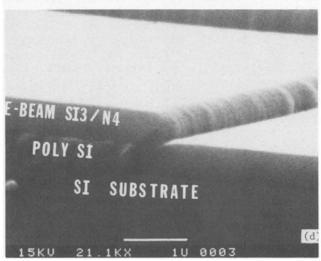

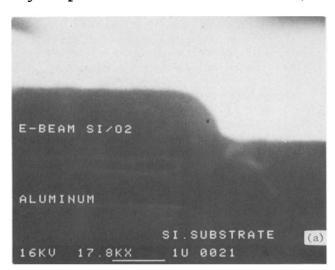

Figure 1 (a,b,c,d,) shows electron beam deposited  $SiO_2$  and  $Si_3N_4$  films conformally covering both aluminum and polysilicon patterns. A slight cusping of the 0.5  $\mu m$  SiO<sub>2</sub> film in figure 1b at the base of the polysilicon step is evident. Optimization of the deposition conditions to reduce cusping has not been undertaken. Figure 1d depicts smooth Si3N4 coverage to the right of the polysilicon step while coverage on the surface of the step is rough due to the uneven polysilicon. Likewise the electron beam deposited SiO2 and Si3N4 films conformally cover the surface of aluminum steps as in figure la and lc. Film thinning over step sidewalls is less than 10 percent as measured by inspection of the SEM micrographs. Also, no film cracking was visible for all of the SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> layers investigated (0.4 μm to 5 μm thick).

## Acknowledgement

This work was supported by the National Science Foundation, the Office of Naval Research, and NASA-Lewis. We thank Hewlett Packard, Loveland, CO for providing the patterned wafers and access to the SEM.

## REFERENCES

- L. R. Thompson, J. J. Rocca, K. Emery,

P. K. Boyer, and G. J. Collins, Appl.

Phys. Lett., 43, 777, 1983.

- D. Bishop, J. J. Rocca, K. Emery,

L. Thompson, and G. J. Collins, to be published, Appl. Phys. Lett.

- K. Emery, L. R. Thompson, D. Bishop,

P. K. Boyer, H. Zarnani, J. J. Rocca,

C. A. Moore, and G. J. Collins, Materials

Research Society, November 14-16, 1983,

Boston, MA.

\*Electrochemical Society Student Member.

\*\*Present address: Hewlett-Packard, Loveland,

CO.

Colorado State University assisted in meeting the publication costs of this article.

Fig. 1. SEM photographs of electron beam deposited  $\rm SiO_2$  and  $\rm Si_3N_4$  over 8000 Å Al and 4000 Å poly-Si steps. A, above: 1  $\mu m$   $\rm SiO_2$  over Al. B, top right: 0.5  $\mu m$   $\rm SiO_2$  over poly-Si. C, center right: 1  $\mu m$   $\rm Si_3N_4$  over Al. D, bottom right: 1  $\mu m$   $\rm Si_3N_4$  over Al.