#### DISSERTATION

#### GENERALIZED FULL SPARSE TILING OF LOOP CHAINS

Submitted by

Christopher D. Krieger

Department of Computer Science

In partial fulfillment of the requirements for the Degree of Doctor of Philosophy Colorado State University Fort Collins, Colorado Fall 2013

#### Doctoral Committee:

Advisor: Michelle Mills Strout

Wim Böhm Sanjay Radjopadhye Jennifer Mueller

#### ABSTRACT

#### GENERALIZED FULL SPARSE TILING OF LOOP CHAINS

Computer and computational scientists are tackling increasingly large and complex problems and are seeking ways of improving the performance of their codes. The key issue faced is how to reach an effective balance between parallelism and locality. In trying to reach this balance, a problem commonly encountered is that of ascertaining the data dependences. Approaches that rely on automatic extraction of data dependences are frequently stymied by complications such as interprocedural and alias analysis. Placing the dependence analysis burden upon the programmer creates a significant barrier to adoption.

In this work, we present a new programming abstraction, the *loop chain*, that specifies a series of loops and the data they access. Given this abstraction, a compiler, inspector, or runtime optimizer can avoid the computationally expensive process of formally determining data dependences, yet still determine beneficial and legal data and iteration reorderings.

One optimization method that has been previously applied to irregular scientific codes is full sparse tiling. Full sparse tiling has been used to improve the performance of a handful of scientific codes, but in each case the technique had to be applied from scratch by an expert after careful manual analysis of the possible data dependence patterns. The full sparse tiling approach was extended and generalized as part of this work to apply to any code represented by the loop chain abstraction. Using only the abstraction, the generalized algorithm can produce a new data and iteration ordering as well as a parallel execution schedule.

Insight into tuning a generalized full sparse tiled application was gained through a study of the different factors influencing tile count. This work lays the foundation for an efficient autotuning approach to optimizing tile count.

#### ACKNOWLEDGEMENTS

I gratefully acknowledge support for this research from the Department of Energy CACHE Institute grant DE-SC04030, DOE grant DE-SC0003956, and NSF grant CCF 0746693. This research utilized the CSU ISTeC Cray HPC System supported by NSF Grant CNS-0923386. I also acknowledge the use of the machines in Intel's Manycore Testing Lab.

I also appreciate the feedback and support received throughout my graduate career from my fellow students Andy Stone, Chris Wilcox, Tomofumi Yuki, and Alan LaMielle, as well as from faculty members Cathie Olschanowsky, Sanjay Rajopadhye, and Wim Böhm.

I thank Samantha Wood for her work on full sparse tiling the matrix powers kernel and her invaluable SMOReS thesis, which was frequently consulted when analyzing the behavior of different sparse matrices.

I am also thankful for the patience and understanding of my colleagues at Intel, Ram Srinivasan, Jim Callister, Stephanie Postal, Richard Blumburg, Alex Settle, Lambert Schaelicke, Eric Borch, and Derek Cho. Their unflagging support contributed significantly to my ability to work on my research while continuing my career.

While developing the loop chain abstraction, I received valuable feedback and code examples from Xinfang Gao and Stephen Guzak of the Colorado State University Mechanical Engineering Department and from Brian Van Straalen and Sam Williams of Lawrence Berkeley National Lab.

I appreciate the help of my collaborators Paul HJ Kelly, Doru Bercea, Fabio Luporini, and Graham Markall at Imperial College of London, Carlo Bertolli at IBM Research, and Gihan Mudalige at Oxford College. Our discussions on full sparse tiling unearthed many weaknesses in early versions of the generalized full sparse tiling algorithm. I also thank them for their support regarding the airfoil benchmark.

#### **DEDICATION**

I give special thanks to my advisor, Michelle Strout, who was willing to advise, against her better judgement, a student attempting to live the oxymoron "part time PhD student." Her years of guidance, teaching, and patience with my non-standard and protracted graduate program is much appreciated.

I dedicate this work to my wife Lockey and our four sons Ian, Thomas, Jacob, and Eli. The original dedication in my master's thesis read, "To Lockey, who kept this a thesis and not a dissertation," reflecting her desire to be done with graduate school. Now, after more than a decade and over six more years of schooling, she finally has her wish.

### TABLE OF CONTENTS

| Al | BSTR                               | RACT                                                                           | ii  |  |  |

|----|------------------------------------|--------------------------------------------------------------------------------|-----|--|--|

| A  | CKNO                               | OWLEDGEMENTS                                                                   | iii |  |  |

| Dl | EDIC                               | ATION                                                                          | iv  |  |  |

| 1  | Intro                              | oduction                                                                       | 1   |  |  |

|    | 1.1                                | Balancing Parallelism and Locality in Scientific Codes                         | 1   |  |  |

|    | 1.2                                | Existing Approaches to Balancing Parallelism and Locality                      | 2   |  |  |

|    | 1.3                                | Introduction to Loop Chains                                                    | 4   |  |  |

|    | 1.4                                | Introduction to Full Sparse Tiling                                             | 8   |  |  |

|    | 1.5                                | Problems with Single Purpose Approaches to Full Sparse Tiling                  | 9   |  |  |

|    | 1.6                                | Generalized Full Sparse Tiling                                                 | 11  |  |  |

|    | 1.7                                | 7 Understanding the Impact of Tile Size and Parallelism Under Generalized Full |     |  |  |

|    |                                    | Sparse Tiling                                                                  | 12  |  |  |

|    | 1.8                                | Summary of Contributions                                                       | 13  |  |  |

| 2  | Loop Chain Programming Abstraction |                                                                                |     |  |  |

|    | 2.1                                | Motivation for the Loop Chain Abstraction                                      | 16  |  |  |

|    | 2.2                                | Formal Definition of the Loop Chain Abstraction                                | 18  |  |  |

|    |                                    | 2.2.1 Iteration Spaces                                                         | 18  |  |  |

|    |                                    | 2.2.2 Data Spaces                                                              | 20  |  |  |

|    |                                    | 2.2.3 Data Access Relations                                                    | 20  |  |  |

|    | 2.3                                | Methods for Specifying Loop Chains                                             | 22  |  |  |

|    |                                    | 2.3.1 Application Programming Interfaces                                       | 22  |  |  |

|    |                                    | 2.3.2 Pragmas                                                                  | 23  |  |  |

|    |                                    | 2.3.3 Domain Specific Languages                                                | 24  |  |  |

|    | 2.4                                | Optimizations Enabled by Loop Chains                                           | 26  |  |  |

|    | 2.5                                | Examples of Loop Chains Present in Existing Scientific Codes                   | 28  |  |  |

|   | 2.6  | Prior    | Work Related to Loop Chains                              | 31 |

|---|------|----------|----------------------------------------------------------|----|

|   |      | 2.6.1    | Programming Models Using User Defined Tasks              | 31 |

|   |      | 2.6.2    | Automatic Approaches for Task Detection                  | 33 |

|   |      | 2.6.3    | Communication Avoidance                                  | 33 |

|   | 2.7  | Limita   | ations of Loop Chains                                    | 34 |

| 3 | Gen  | eralized | Full Sparse Tiling                                       | 37 |

|   | 3.1  | Prior    | Single Purpose Approaches to Full Sparse Tiling          | 37 |

|   | 3.2  | Issues   | With Generalization of Full Sparse Tiling                | 39 |

|   |      | 3.2.1    | Complexity of Data Dependency Computation                | 39 |

|   |      | 3.2.2    | Handling Parallel Reductions                             | 44 |

|   |      | 3.2.3    | Dependences Between Non-Adjacent Loops                   | 44 |

|   |      | 3.2.4    | Complexity of Creating the Initial Partitions            | 45 |

|   | 3.3  | Gener    | al Full Sparse Tiling Algorithm                          | 46 |

|   |      | 3.3.1    | The Top Level Full Sparse Tiling Algorithm               | 48 |

|   |      | 3.3.2    | Partitioning of the Seed Iteration Space                 | 52 |

|   |      | 3.3.3    | Tracking Data Reads and Writes                           | 53 |

|   |      | 3.3.4    | Backward and Forward Tiling Algorithms                   | 54 |

|   |      | 3.3.5    | Task Graph Generation                                    | 62 |

|   | 3.4  | Validi   | ty of the General Full Sparse Tiling Algorithm           | 64 |

|   | 3.5  | Other    | Parallelization Approaches Related to Full Sparse Tiling | 65 |

| 4 | Loca | ality Co | onsiderations For Full Sparse Tiling                     | 68 |

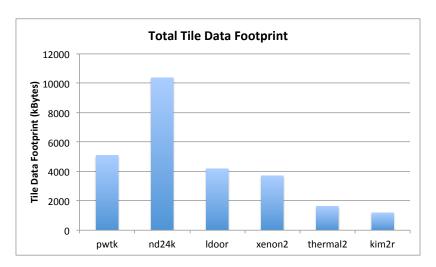

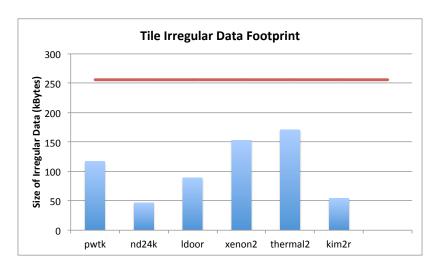

|   | 4.1  | Intera   | ction Between Locality and Full Sparse Tiling            | 69 |

|   |      | 4.1.1    | Iteration Placement To Improve Locality                  | 69 |

|   |      | 4.1.2    | Relationships Between Tile Footprints and Cache Sizes    | 71 |

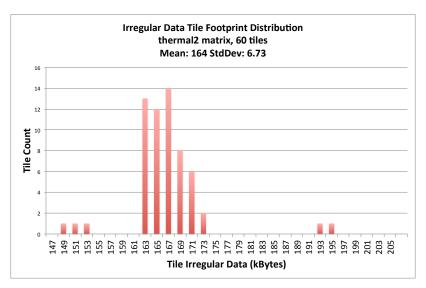

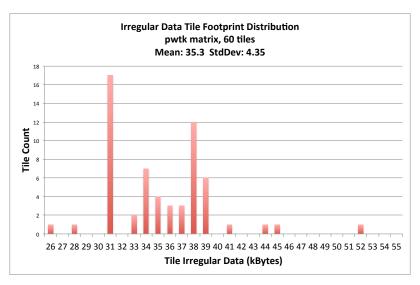

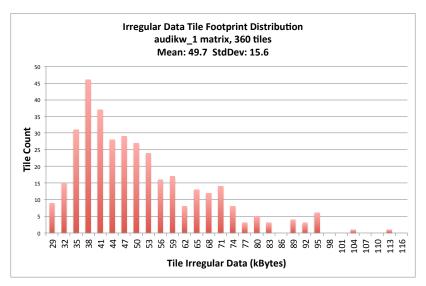

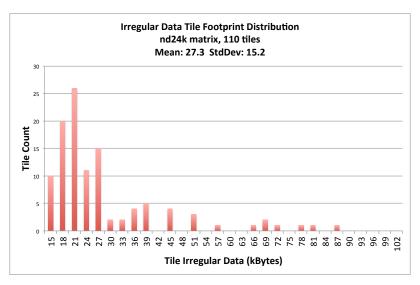

|   |      | 4.1.3    | Distributions of Tile Memory Footprints                  | 72 |

|   | 4.2  | Partit   | ioning the Seed Space to Improve Temporal Locality       | 75 |

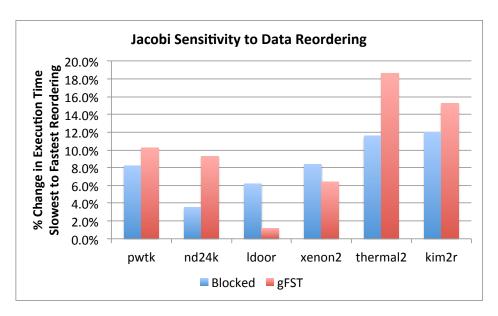

|   | 4.3  | Data 1   | Reordering and Generalized Full Sparse Tiling            | 78 |

| Э | Para                      | allelism Considerations for Full Sparse Tiling                         | 81  |  |  |

|---|---------------------------|------------------------------------------------------------------------|-----|--|--|

|   | 5.1                       | Coloring Seed Partitions To Improve Parallelism                        | 81  |  |  |

|   | 5.2                       | Issues with Measuring and Controlling Task Graph Parallelism           | 84  |  |  |

|   |                           | 5.2.1 Statistics for Measuring Parallelism                             | 84  |  |  |

|   |                           | 5.2.2 Using Tile Count to Control Parallelism                          | 85  |  |  |

|   | 5.3                       | Determining the Optimal Amount of Parallelism                          | 87  |  |  |

| 6 | Com                       | npeting Forces In Optimization of Generalized Full Sparse Tiling       | 97  |  |  |

|   | 6.1                       | Impact of Scheduling Overhead                                          |     |  |  |

|   | 6.2                       | Impact of Locality Dilution                                            |     |  |  |

|   | 6.3                       | B Impact of Tile Irregular Data Footprint                              |     |  |  |

|   | 6.4                       | Impact of Parallelism and Load Imbalance                               |     |  |  |

|   | 6.5                       | Interaction of Forces                                                  | 106 |  |  |

| 7 | The                       | Generalized Reordering Optimizer for Ubiquitous Tiling (GROUT) Library |     |  |  |

|   | and Programming Interface |                                                                        |     |  |  |

|   | 7.1                       | Specifying the Elements of a Loop Chain                                | 108 |  |  |

|   |                           | 7.1.1 Iteration Spaces                                                 | 110 |  |  |

|   |                           | 7.1.2 Data Spaces                                                      | 110 |  |  |

|   |                           | 7.1.3 Data Access Relations                                            | 111 |  |  |

|   |                           | 7.1.4 Loop Bodies                                                      | 113 |  |  |

|   |                           | 7.1.5 Loops and Loop Chains                                            | 116 |  |  |

|   | 7.2                       | Applying Optimizations Using Inspectors                                | 117 |  |  |

|   | 7.3                       | Executing Loop Chains Using Executors                                  | 118 |  |  |

|   | 7.4                       | A Complete Example Using GROUT                                         | 119 |  |  |

| 8 | Con                       | clusions And Future Research                                           | 122 |  |  |

|   | 8.1                       | Conclusions                                                            | 122 |  |  |

|   | 8.2                       | Areas Identified for Further Research                                  | 194 |  |  |

|     | 8.2.1 | Full Sparse Tiling for Distributed Memory Systems           | 124 |

|-----|-------|-------------------------------------------------------------|-----|

|     | 8.2.2 | Extending Domain Specific Languages To Define Loop Chains   | 125 |

|     | 8.2.3 | Locality Improvements to the Generalized Full Sparse Tiling |     |

|     |       | Algorithm                                                   | 126 |

| 8.3 | Summ  | arv                                                         | 127 |

## Chapter 1

## Introduction

Computer and computational scientists are tackling increasingly large and complex problems and are seeking ways of improving the performance of their codes. One of the key issues faced by these scientists and others in the high performance computing community is how to reach an effective balance between parallelism and locality. The general solution is to bundle together work that uses the same data, thereby improving locality. That work then executes according to a parallel schedule that respects all data dependences. Many different solutions, each with its advantages and disadvantages, have been proposed but the issue remains an area of active research.

A challenge commonly encountered by existing approaches is how to ascertain the data dependences. Approaches that rely on automatic extraction of data dependences are frequently stymied by complications such as interprocedural program analysis and alias analysis. Placing the dependence analysis burden upon the programmer creates a significant barrier to adoption.

In this work, we present a new programming abstraction, *loop chains*, that allows programmers or tools to specify a series of loops and the data they access. Declaring what data is accessed by a loop is far simpler than determining data dependences. Working from this abstraction, a generalized version of the full sparse tiling approach is then able to create high locality, parallel schedules.

# 1.1 Balancing Parallelism and Locality in Scientific Codes

There is a significant, established code base in the scientific computing community. To date, many of these codes have been parallelized. However, these parallel codes are now

encountering scalability issues due to poor data locality, inefficient data distributions, and/or load imbalance as they are run on larger and larger systems. Code and algorithm changes are therefore necessary in order to effectively utilize new computational resources, many of which require ever increasing levels of parallelism for efficient execution.

With the increase in the amount of computational power has come an increased need for memory bandwidth to supply those resources with data. However, memory technology has not kept pace with advances in computation rate. This has led to an imbalance between the compute capabilities of multicore systems and accelerators and the ability of the memory subsystem or interconnect network to deliver data. To address this problem, codes are being modified to reduce their bandwidth requirements, often by improving data locality. This often requires changes to data and work distribution methodologies.

Given this shifting landscape of increasing compute power, often from sources such as accelerators, diminishing relative performance of memory systems, and large amounts of critical, validated scientific codes with rigid explicit data distributions yielding non-portable performance, it is no surprise that balancing parallelism and locality remains a significant challenge for the scientific computing community.

# 1.2 Existing Approaches to Balancing Parallelism and Locality

Various solutions have emerged for addressing the challenge of achieving and balancing both parallelism and data locality. One current approach is the incremental addition of parallelism using OpenMP [23] parallel loop pragmas. In this approach, the compiler adds the necessary code for parallel execution and synchronization. This method enables the unobtrusive addition of parallelism. Unfortunately, this approach typically provides the programmer with little control over how data and computation are grouped or distributed. For example, OpenMP only allows statically or dynamically sized blocks of contiguous iterations to be assigned to threads. Good data locality is only obtained if consecutive iterations of a loop access data in common or can be made to do so. OpenMP also does not provide a way to

group iterations of different loops together. These limitations make it difficult to improve data locality during parallel execution.

An earlier and still quite popular approach to parallelization that is significantly less incremental is to use explicit message passing libraries such as MPI [33]. MPI has been used to parallelize a significant fraction of mature parallel scientific codes. MPI development is disruptive and requires a considerable coding effort. However, the difficult aspects of the MPI programming model also lead to advantages in terms of data locality. Specifically, the programmer must manage the distribution for both the data and the computation and specify communication between nodes with explicit sends and receives. The programmer can therefore put computation together that accesses similar data.

Both OpenMP and MPI programming models have led to codes with one parallel loop after another in sequence. Communication among processing elements typically occurs between loops. At its simplest, this bulk model can be synchronized using barriers. Unfortunately, this approach can be inefficient if different processing elements take different amounts of time to complete their assigned work. This is usually the case when work cannot be evenly divided between processors or if execution times differ due to varying data access times. In this case, processors sit idle, waiting until the last processor completes its work and reaches the barrier.

In order to achieve the high levels of parallelism required to efficiently execute on large parallel machines, it is necessary to move from this bulk parallelism to asynchronous parallelism. With asynchronous parallelism, the ordering dependences between tasks are determined either in advance or dynamically at runtime. A task is allowed to execute immediately upon the completion of all its predecessor tasks. This model circumvents many of the load balancing issues of bulk synchronization. Models such as the OpenMP 3.0 task model [30], the Concurrent Collections model [17], and StarPU [3] directly expose asynchronous tasks.

Other approaches to managing the parallelism and data locality tradeoff include Partitioned Global Address Space (PGAS) languages such as Unified Parallel C [31] or Co-Array Fortran [47]. In these languages, users explicitly distribute data to nodes and can therefore

achieve good locality, just as was done using direct MPI calls to distribute data. These languages have the advantage that the necessary communication code is abstracted away behind a one-sided communication model. In this model, accessing remote data is coded in a way that is syntactically similar to local accesses and a compiler inserts the necessary data transfers. Consequently, while data distribution is still explicitly under programmer control, communication is not as cumbersome in a PGAS language. Unfortunately, PGAS languages have no language features to improve data locality across loops within a node.

Relatively new parallel programming languages such as Chapel [15] or X10 [18] provide mechanisms for specifying data locality such as places and locales, but these specifications are done on a loop by loop or computation by computation basis. The parallel constructs are considered in isolation with respect to other adjacent or surrounding constructs. There is no way to aggregate parallel loops. There is also a prohibitive cost in porting existing code to an entirely new language.

At the opposite end of the spectrum lie autoparallelization [4, 32] approaches. Under these schemes, a compiler or other tool determines the data and computation distribution automatically. Examples such as the Build To Order BLAS compiler perform data locality and parallelization optimizations across function calls [9]. An autoparallelization approach can achieve good performance portably and frees the programmer from having to make fixed choices, but also means the programmer has little ability to alter or further optimize the distributions. More significantly, automatic approaches typically rely on extensive data dependence analysis. Precise data dependence analysis is an open research challenge, fraught with difficulties such as pointer aliasing and interprocedural analysis that historically have forced these algorithms to make overly conservative assumptions on real-world codes.

## 1.3 Introduction to Loop Chains

Given the extremes of user-laborious, non-portable parallelization approaches or limited automatic methods previously outlined, it seems that the best answer lies between the two. Ideally, the scheduling and placement of computation and distribution of data would be handled automatically by a compiler and/or runtime that is aware of the target system and can optimize for it. However, it is important for such a system not to rely heavily on the automatic detection of data dependences, especially across the many procedure calls that occur in modular scientific computing software.

One way to eliminate the need for automatic dependence analysis is to require the programmer to provide this information. Unfortunately, in general, and particularly in irregular codes, the programmer does not reason about the code in terms of formal data dependences between loop iterations. Even more rarely does the programmer consider dependences across different loops. What is needed is a way for the data dependences to be expressed in a way that is easily understood by a programmer and fits with his or her intuition about the code.

In this work, we introduce a new abstraction called a *loop chain* in which a sequence of parallel and/or reduction loops that explicitly share data are grouped together into a chain. A description of the data accessed within each loop is provided as part of the abstraction. The loop chain stands at an intermediate point, still close enough to the concrete code that the programmer can reason about it, yet also close enough to the explicit data dependences that the optimizer can derive ordering constraints from it.

The definition of a loop chain consists of three pieces, namely:

- Well defined iteration spaces for each loop,  $\{L_0, L_2, \dots, L_{N-1}\}$

- Data spaces for accessed data,  $\{D_0, D_2, \dots, D_{M-1}\}$

- $\bullet$  Access relations for data read/written by each iteration of each loop:

$$R_{L_l \to D_d}(\vec{i})$$

or  $W_{L_l \to D_d}(\vec{i})$

Note that because the loop chain abstraction requires the explicit declaration of data access relations, it is not dependent on automatic techniques or interprocedural program analysis to discover data dependences. Because the iteration spaces are well defined, every iteration of every loop is clearly defined in the loop chain. Satisfying producer-consumer relationships for data imposes a partial ordering on the execution sequence of the iterations.

```

\begin{array}{lll} \mathbf{for} & (\mathbf{int} & t = 0; & t < \text{numIters}; & t += 2) & \{\\ & \mathbf{for} & (\mathbf{int} & i = 0; & i < \text{numrows}; & i ++) & \{ \end{array}

3

double diag = 1.0;

Ueven [i] = 0.0;

for (int p=IA[i]; p < IA[i+1; p++) {

6

int j = JA[p];

if (j=i) {diag = A[p];}

else { Ueven[i] += A[p] * Uodd[j]; }

10

Ueven[i] = (F[i] - Ueven[i]) / diag;

11

12

13

for (int i=0; i<numrows; i++) {

double diag = 1.0;

14

Uodd[i] = 0.0;

15

16

for (int p=IA[i]; p < IA[i+1]; p++) {

17

int j = JA[p];

if (j=i) \{ diag = A[p]; \}

18

19

else { Uodd[i] += A[p] * Ueven[j]; }

20

21

Uodd[i] = (F[i] - Uodd[i]) / diag;

22

23

```

Figure 1.1: The kernel of the sparse Jacobi solver for CSR sparse matrices. Output vectors Ueven and Uodd are used in an alternating, ping-pong, fashion. The loops beginning on lines 2 and 13 can be chained.

Therefore, once specified, a loop chain can be used to derive a set of loop iterations under a partial ordering. This partially ordered set of iterations makes scheduling and determining data distributions across loops possible for a compiler and/or run-time system. The flexibility of being able to schedule across loops enables better management of the data locality and parallelism tradeoff.

The concept of a loop chain can be illustrated with a concrete example. Figure 1.1 shows the C code for a sparse Jacobi solver. Given a sparse matrix A, and a vector  $\vec{f}$ , related by  $A\vec{u} = \vec{f}$ , each iteration of the sparse Jacobi method produces an approximation to the unknown vector  $\vec{u}$ . The recurrence equation closely resembles matrix vector multiplication and is representative of a broad class of sparse linear algebra applications. This code uses a pingpong approach to the output vector, switching between Ueven and Uodd. The outermost loop repeats the kernel for a fixed number of repetitions.

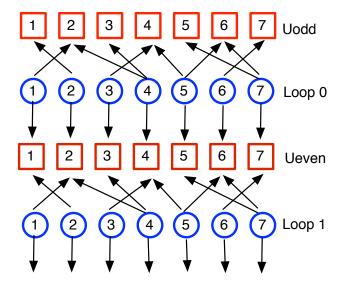

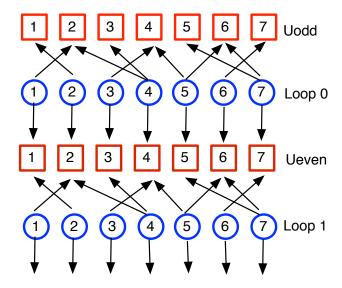

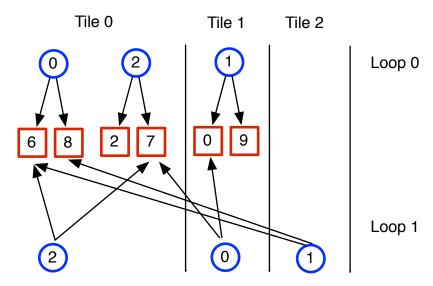

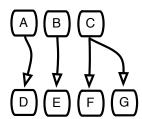

If the two loops shown on lines 2 and 13 are combined into a loop chain, they form a chained iteration space like that shown in Figure 1.2. The specific space shown is for a sample matrix with seven rows and columns. In Figure 1.2, the boxes represent data spaces or arrays

Figure 1.2: The data and iteration space view of the Jacobi code in Figure 1.1. The boxes represent the Ueven and Uodd vectors, the circles represent iterations of the two loops. The data access functions are represented by arrows. The upward pointing read arrows are irregular and dictated by the particular sparse matrix, while the downward pointing write accesses are an identity relation. Chain invariant data, such as F, IA, JA, and A, are present in the loop chain data structures but are omitted from this diagram.

$D_0$ =Ueven and  $D_1$ =Uodd, while the circles represent iterations of the loops beginning on lines 2 and 13. The sparse matrix used as input is

$$A = \begin{bmatrix} 1 & 2 & 0 & 0 & 0 & 0 & 0 \\ 4 & 3 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 6 & 2 & 0 & 0 & 0 \\ 0 & 9 & 2 & 2 & 0 & 0 & 0 \\ 0 & 0 & 0 & 8 & 2 & 5 & 0 \\ 0 & 0 & 0 & 0 & 0 & 2 & 1 \\ 0 & 0 & 0 & 0 & 1 & 4 & 7 \end{bmatrix}. \tag{1.1}$$

The iteration spaces shown for the two loops are  $L_0 = \{1, 2, ..., 7\}$  and  $L_1 = \{1, 2, ..., 7\}$ , which is the case for the given sparse matrix with 7 rows. Arrows represent the data access relations, with upward pointing arrows indicating the data reads  $R_{L_0 \to D_1} = R_{L_1 \to D_2} = \{[1] \to [2], [2] \to [1], [3] \to [4], [4] \to [2], [4] \to [3], [5] \to [4], [5] \to [6], [6] \to [7], [7] \to [5], [7] \to [6]\}$  and downward pointing arrows indicating the identity relation for data writes  $W_{L_0 \to D_2} = W_{L_1 \to D_1} = \{[1] \to [1], [2] \to [2], [3] \to [3], [4] \to [4], [5] \to [5], [6] \to [6], [7] \to [7]\}.$

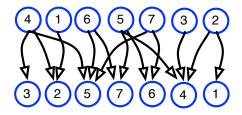

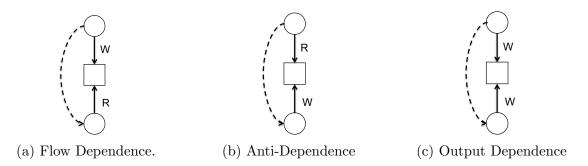

Given the loop chain abstraction of the Jacobi solver code, generating the partially ordered set of iterations is a straightforward process. The result is shown in Figure 1.3. Any

Figure 1.3: Partial ordering of iterations in the Jacobi loop chain

schedule for the loops in the loop chain that respects the partial ordering shown will be valid. This gives tremendous flexibility to the compiler, or in this case the runtime system to manipulate the iteration orderings to achieve a target mix of parallelism and data locality.

## 1.4 Introduction to Full Sparse Tiling

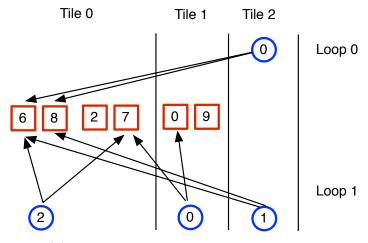

Given a loop chain and the implicit iteration partial ordering, the next step in generating a high performing schedule is selecting an iteration grouping and ordering that provides adequate parallelism while maximizing data locality. Full sparse tiling [55, 53] (FST) is a technique for accomplishing that goal. Full sparse tiling aims to cluster together iterations that access data in common, even across different loops in the loop chain. This converts eventual data reuse into more immediate data reuse, thereby improving temporal locality and in turn improving performance due to an improved cache hit rate. These iteration clusters are called *sparse tiles*. There is a partial ordering on when sparse tiles can execute relative to one another, which is simply an aggregation of the orderings imposed on individual iterations due to the data dependences captured by the data access relations. The partial ordering of sparse tiles can be expressed as a *task graph*.

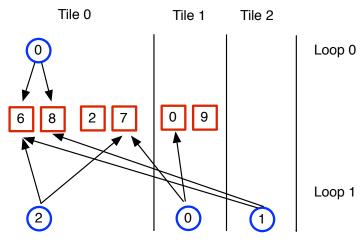

Different full sparse tilings of loop chain iterations can vary the number of iteration clusters, called *sparse tiles*, used in the execution schedule. Schedules with fewer, and therefore larger, sparse tiles may have better locality than smaller tiles. Schedules with more tiles generally exhibit greater parallelism. Thus, by carefully constructing the tiles and controlling their size, full sparse tiling can balance parallelism and locality as appropriate for a given hardware system.

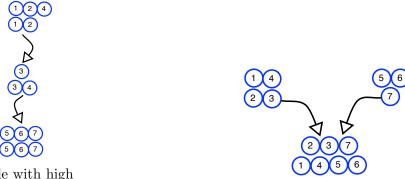

(a) A schedule with high locality and low parallelism.

(b) A schedule with more balanced locality and parallelism.

Figure 1.4: Different full sparse tilings yield different amounts of parallelism and locality.

Examples of some of the full sparse tilings possible for the loop chain presented in Figure 1.2 are given in Figure 1.4. The schedule shown in Figure 1.4a has excellent data reuse between iterations within a tile. However, only one tile can be executed at a time. The schedule shown in Figure 1.4b maintains some locality, but initially permits two tiles to execute in parallel. These are only two possibilities along the broad spectrum of possible full sparse tilings. To select between the different possible schedules, a human can manually evaluate the performance of different schedules and select the highest performing one. Alternatively, schedules can be selected based on predictions from a performance model or an autotuning approach can be used.

# 1.5 Problems with Single Purpose Approaches to Full Sparse Tiling

Previous to this work, each application of full sparse tiling was implemented for a specific type of code. For example, full sparse tilers were written for the MolDyn molecular dynamics simulator [53], a Jacobi solver such as was described in Section 1.3 [40], a Gauss-Seidel solver [54], and a matrix powers kernel [57, 25, 46]. Each of these tilers was developed largely from scratch and took considerable development effort. There was very little, if any, code reuse between the full sparse tilers. This led to a variety of code maintenance issues and unnecessary duplication of effort.

Because each tiler was purpose-built for a specific application, the tilers took advantage of properties of the given application to make assumptions about the tiling problem. For example, the Jacobi solver was written with the understanding that all vector writes would be done with an identity access pattern and that all read accesses would be specified by the non-zero pattern in the sparse matrix. These assumptions were valid and resulted in tiling code that, while inappropriate for other applications, was considerably simplified. However, in some cases, even a slight deviation from the original assumptions would result in invalid schedules being generated. For example, if a non-symmetric matrix were given to the Jacobi code, the tiler would ignore some storage related dependences and could sequence iterations illegally.

Similarly, assumptions were also made while writing the custom full sparse tiling code for the MolDyn molecular dynamics simulation. This simulation code consists of three loops in the loop chain. The first and last loops access memory through identity updates. It is only the center loop that has irregular accesses. Given this pattern, the custom code was able to partition the center loop and then assign iterations of the outer loops to tiles in a straightforward manner. This generates correct serial schedules. However, when these schedules were parallelized using the Jacobi task graph generation code directly, potentially illegal schedules were produced. This is because the Jacobi task sequencer does not consider reduction dependences within a loop, a situation that does not arise in the Jacobi solver but that is present in the center loop in MolDyn.

Finally, tile sizes resulting in optimal performance were determined for each application, and in some cases, for each input set, in an ad hoc fashion. These were usually determined through manual search, perhaps directed by a heuristic that made many simplifying assumptions. For example, some tile size selection code assumes that a seed partition's footprint should be equal to one-eighth of the mid level cache [54]. From this fixed starting point, the user would repeatedly run the application, making adjustments to the tile size until good performance was attained.

Experience with these application-specific full sparse tilers led to several conclusions. First, significant performance improvements, in some cases exceeding 50%, can be achieved by full sparse tiling [42]. However, it was also clear that writing a full sparse tiler is a laborious process that requires expert knowledge of tiling as well as domain knowledge. Second, little code could be reused between efforts due to deeply rooted assumptions that did not hold in other applications. Lastly, each of the tiler's parameters had to be tuned for the specific application in order to achieve sizable performance gains. No formal algorithm existed for finding the best performance for a given processor, core count, memory hierarchy, and scientific application. These problems together formed a formidable barrier to widespread adoption of full sparse tiling approaches.

## 1.6 Generalized Full Sparse Tiling

A major contribution of this research effort is the creation of a generally applicable full sparse tiling algorithm. As a precursor to designing such an algorithm, we identified several areas in which prior individual approaches were not general.

First, the efforts relied on pieces of the problem being described or specified in a particular way. For example, much of the Jacobi full sparse tiler depends on the data access pattern being described by the non-zeros within a compressed sparse row (CSR) formatted sparse matrix. Any problem in which dependences are not expressed as a sparse matrix immediately encounters incompatibilities.

Furthermore, a general full sparse tiler cannot assume a particular pattern or number of loops, nor can it rely on a specific type of data dependence between loops. It must be able to take all types of dependences into consideration, including storage related anti-, input, and output dependences.

In addition, if tiles are to be executed in parallel, dependences between tiles must also be understood. This therefore requires that the partial ordering between tiles, typically represented as a task graph, must honor an aggregation of the individual iteration dependences. In addition, the tiles must also be ordered to respect reduction dependences, even though

these dependences do not contribute to the partial ordering between loop iterations in a serial schedule.

Our general full sparse tiling algorithm was developed to squarely addresses these issues. A central feature of the algorithm is that it tiles code that has been expressed as a loop chain. No additional requirements are imposed as to the structure of the code and no additional information is needed. By using loop chains as an intermediary abstraction between the original code and the full sparse tiling algorithm, many of the pitfalls to generality that ensnared previous full sparse tiling efforts are neatly avoided.

Given a loop chain, the general algorithm is able to respect all types of data dependences, including storage related dependences and reduction dependences that were not explicitly analyzed in previous work. These dependences are completely derived from the data access relations and relative placement of loops as described in the loop chain. The algorithm accounts for all dependences while creating a serial schedule as well as a parallel task graph schedule. A complete description of the general full sparse tiling algorithm is presented in Chapter 3.

## 1.7 Understanding the Impact of Tile Size and Parallelism Under Generalized Full Sparse Tiling

Selecting the proper balance of parallelism and locality while full sparse tiling is an extremely challenging problem. Both parallelism and locality are heavily influenced by the number of tiles used when full sparse tiling, precluding the independent optimization of these two factors. If the task graph has low parallelism, particularly if the parallelism is lower than the number of cores available, the execution will be restricted to a subset of the total cores and therefore will have limited scalability. Likewise, if the average tile memory footprint greatly exceeds the target size, usually related to the size of a hardware cache, performance improvements will not be fully realized. This is due to the tile working set being larger than what can be supported by the cache hierarchy. In this case, while full sparse tiling improves locality, it does not sufficiently shorten the reuse distance of data to be smaller than the

cache size. Therefore, some understanding of the interaction between, or relative priority or importance of, parallelism and locality is useful when optimizing performance.

This work studies what metrics should be used when discussing and optimizing the tile size for improved locality. It also examines how the amount of parallelism in a task graph should be expressed. In addition to determining to what properties task graph execution time is sensitive, we also develop guidelines for balancing between locality and parallelism when selecting the tile count for a generalized full sparse tiling of a loop chain.

## 1.8 Summary of Contributions

This work spans a variety of important contributions, most of which are presented in greater detail later in this dissertation. Here is a succinct summary of the more significant items.

#### 1. The Loop Chain Abstraction

- (a) A formal definition of a new programming construct called a *loop chain*.

- (b) A presentation of possible mechanisms for specifying the loop chaining. abstraction using libraries, domain specific languages, and pragmas.

- (c) A complete C++ loop chaining library and application programming interface for specifying loop chains.

#### 2. Generalization of the Full Sparse Tiling Algorithm

- (a) A formal definition of generalized full sparse tiling for any loop chain that encompasses reduction and storage related dependences as well as flow dependences.

- (b) A C++ library that applies full sparse tiling to loop chains specified using the loop chain API.

- (c) Additional supporting algorithms and code:

- i. A novel graph partitioning algorithm, ParCubed, that is fast and parallelized for shared memory.

- ii. A novel hypergraph partitioning algorithm, HyperParCubed, that is fast and parallelized for shared memory.

- iii. A task graph execution engine for shared memory that builds upon the following existing parallel models:

- A. Intel's Concurrent Collections programming model,

- B. OpenMP parallel for loops,

- C. OpenMP 3.0 tasks,

- D. Cilk Plus spawn/sync language extensions,

- E. pThreads library,

- F. Intel's Threading Building Blocks flow graphs

- 3. A study of the forces affecting performance of a generalized full sparse tiled Jacobi solver including:

- (a) The identification of irregular data footprint and median parallelism as important metrics for understanding performance in the context of generalized full sparse tiling.

- (b) A study of the correlation between performance of generalized full sparse tiled code and cache size.

- (c) Guidelines for selecting the amount of parallelism and the best irregular data footprint for optimal execution.

This dissertation work is a comprehensive effort to remove barriers to the wider adoption of full sparse tiling. Unlike previous full sparse tiling implementations, thanks to its use of loop chains, this work is useable by scientific domain experts and other programmers who are not specifically trained in parallel program optimization. A sparse tiling is automatically generated and relative tile dependences are captured in a task graph. This resulting graph is then executed in shared memory using the task graph executors specifically developed as part of this work. Thus, this dissertation is a complete sparse tiling package, from facilitating

a programmer's specification of a loop chain to generation of an optimized parallel schedule to efficient execution of the loops.

## Chapter 2

# Loop Chain Programming Abstraction

Each previous full sparse tiling effort focused on a single application. However, each of these applications had specific properties that made it a good candidate for full sparse tiling. Specifically, each had a series of loops that shared data. Each full sparse tiling research effort developed code and algorithms for analyzing the producer-consumer data dependency chains in that application's sequence of loops. By examining the similarities in these different instances of full sparse tiling, it became apparent that the dependency analysis code could be made general if application specific information describing the loops were expressed in a more abstract and universal fashion. In addition, if this abstraction were carefully designed, it could also be used by a much wider variety of reordering transformations than just full sparse tiling.

In Section 2.1, we further describe our motivation for developing the loop chain abstraction. We then define the abstraction and describe ways for specifying loop chains in Sections 2.2 and 2.3. Optimizations facilitated by loop chains, including, but not limited to, full sparse tiling, are discussed in Section 2.4. Sections 2.5 through 2.7 cover examples of loop chains that naturally occur in scientific codes, a comparison between loop chains and other related approaches, and a review of the limitations of the loop chain abstraction.

## 2.1 Motivation for the Loop Chain Abstraction

Typically, the bulk of the execution time of a scientific application is spent in loops. Thus, optimization efforts understandably focus on decreasing the execution time of these loops. Many of these optimizations consist of scheduling the iterations of the loops to achieve some objective. For example, iterations may be scheduled to improve data locality, minimize communication, or improve parallelism.

Reordering transformations are a class of optimizations that reschedule the execution order of iterations of a loop. In doing so, these transformations must respect the data dependences present in the original code. To do so, the dependences must be determined in some fashion. Approaches that rely on automatic code analysis often encounter challenges such as interprocedural data and pointer alias analysis that forces the use of conservative approximations. These issues can be avoided by requiring the programmer to explicitly enumerate the formal flow, anti, input and output dependences. However, such analysis is tedious, error prone, and is beyond the abilities of many programmers.

In this work, we have developed a new programming abstraction, loop chains, to address the problem of finding data dependences. Within the framework of a loop chain, a programmer specifies what data is accessed by each iteration of a loop through a data access relation. A data access relation is a simple relation from an iteration of a loop to the data elements that are accessed during the execution of that loop iteration. In many cases, this relation can be determined through simple code inspection. For example, for the code: A[i] = k\*B[C[i]], the relation would be from iteration [i] to element [i] of array A and from iteration [i] to element C[i] of array B. Listing data accesses is considerably easier for a programmer to do than to find the explicit data dependences. Having all the data accesses specified circumvents many of the issues that arise during interprocedural or alias analysis. The compiler, runtime, inspector, and/or other optimizer is then able to analyze these data access relations and find a partial ordering on the loop iterations based on the data dependences present in the original code. From these partial orderings, many different legal schedules can be derived. Some schedules can emphasize improved locality, while others provide a large degree of parallelism. Each of these optimized schedules results in a different grouping of the iterations.

To summarize, loop chains provide an incremental interface between programmers and compilers/run-time systems. They formalize and abstract a pattern that already exists in many scientific computing applications and domain-specific libraries. With the information

they provide, compilers and/or run-time systems are able to better balance between data locality and parallelism.

## 2.2 Formal Definition of the Loop Chain Abstraction

The loop chain abstraction consists of an ordered sequence of contiguous loops. Each loop must execute a fixed and known set of iterations. This excludes while loops or loops containing break statements. Additionally, there must not be any code between the loops in a loop chain. Loops in a loop chain must be doall parallel or reductions. There must not be any required ordering of iterations within a loop, such as would result from loop carried data dependences. Finally, there can be no conditional execution of any of the loops in a chain. Loops cannot be guarded with if statements or other statements that alter the control flow of the code. Any sequence of loops that meets these requirements can be expressed as a loop chain.

A loop chain abstracts away much of the detail of the original series of loops. What remains can be described using three components: iteration spaces, data spaces, and data access relations. Iteration spaces concisely describe all the iterations that a compiler or other optimizer must schedule. Similarly, the data spaces describe arrays or other chunks of memory accessed by code within the loop chain. Iterations and data space elements together are the building blocks that are grouped, reordered, or distributed to effect a specific optimization. The data access relations define the relationship between iterations and data. These relations expose not only limitations on iteration reordering due to data dependences but also reveal opportunities to improve locality. The notation used to refer to these components is given in Table 2.1 and each is described in the following sections.

## 2.2.1 Iteration Spaces

Each loop has a well defined iteration space,  $L_0, \ldots, L_{N-1}$ , where N is the number of loops in the chain. In the context of loop chains, the term iteration space refers to the unordered set of executed iterations of a loop body, with each iteration identified by an

Table 2.1: A summary of the symbols used to represent loop chains.

| Symbol Description         |                                                                         |  |  |

|----------------------------|-------------------------------------------------------------------------|--|--|

| L                          | A sequence of loops                                                     |  |  |

|                            | $(L_0, L_1,L_l,L_{N-1}).$<br>An identifier for the $l^{th}$ loop in the |  |  |

| · ·                        | sequence.                                                               |  |  |

| $ L_l $                    | The iteration space associated                                          |  |  |

|                            | with the $l^{th}$ loop in the sequence.                                 |  |  |

| $\vec{i}$                  | A vector that identifies a specific                                     |  |  |

|                            | iteration within a loop.                                                |  |  |

| D                          | A set of data spaces                                                    |  |  |

|                            | $\{D_0, D_1,D_d,D_{M-1}\}.$                                             |  |  |

| $D_d$                      | A specific data space. For exam-                                        |  |  |

|                            | ple, $D_0$ may correspond to a data                                     |  |  |

|                            | array $X$ .                                                             |  |  |

| $ec{d}$                    | A vector that identifies a specific                                     |  |  |

|                            | element within a data space.                                            |  |  |

| $R_{L_l \to D_d}(\vec{i})$ | A relation between iterations and                                       |  |  |

|                            | the data they read.                                                     |  |  |

| $W_{L_l \to D_d}(\vec{i})$ | A relation between iterations and                                       |  |  |

|                            | the data they write.                                                    |  |  |

iteration vector or tuple containing the values of all index variables for that iteration. For example, in the case of a simple for loop: for (i=0; i < 5; ++i) {...},  $L_0$  would refer to the five iterations of the loop,  $L_0 = \{[0], [1], [2], [3], [4]\}$ .

One could define a loop's iteration domain as a contiguous range, a polyhedral set, or an explicitly enumerated set of items. For example, if iterating over the edges of an unstructured mesh, the domain may be defined as  $\{[edge_0], [edge_1], \ldots, [edge_{numEdges-1}]\}$ . Likewise, a container can implicitly define an iteration space as a traversal over all elements in the container. Threading Building Blocks [35], as well as the OP2 unstructured mesh library [11] and the Chombo library [21], both discussed in Section 2.3, all support this type of iteration. The loop chain abstraction does not require that a particular definition of the domain of iterations be used, just that the iteration space domain is well defined.

Observe that an iteration space's set of iterations is unordered. This implies that the original loop must be either doall parallel or else a reduction. There can be no loop carried dependences that impose a relative order on the execution of iterations within a loop. Further note that in the case of iteration spaces, the subscript indicates ordering within the chain, e.g.  $L_0$  precedes  $L_1$  and so forth. This means that any data dependence is between iterations of different loops and that the original ordering of those two loops is known. Taken together, these two requirements greatly simplify dependence analysis. For example, a flow dependence is always from a write in one loop to a read in a higher numbered loop.

#### 2.2.2 Data Spaces

Each data structure accessed within the loop chain must be formally declared as a data space, denoted  $D_0, D_1, \ldots, D_m$ . For data spaces, the subscript numbering does not denote an ordering or placement in a sequence and is only used to uniquely identify the various spaces. Each data space must have a well defined domain. Typical data spaces are one dimensional or multidimensional arrays, though associative arrays, maps, or sets are also possible. Analogous to iteration spaces, a data space refers to a data structure and the complete set of valid indices in the structure's domain or index space. For example, a data space,  $D_0$ , for the ten element array A, would be  $D_0 = \{A[0], A[1], \ldots, A[9]\}$ . While all one dimensional, ten element arrays share the same domain, each would have a unique data space. A data space on a map, paint, indexed by color names might be  $D_1 = \{\text{paint}(red), \text{paint}(green), \ldots, \text{paint}(black)\}$ . Note that the values stored in the referenced data structure are irrelevant and are not part of the data space.

#### 2.2.3 Data Access Relations

As part of a loop chain definition, each loop in the loop chain must declare the data items that are read or written by each iteration of the loop. This is accomplished through the use of data access relations (DARs). Data access relations are mathematical relations between iterations in an iteration space,  $L_l$ , and elements in a data space,  $D_d$ . Read relations

Table 2.2: Enumeration of the data access relations for the example given in Figure 1.2.

| DAR on Loop 1              | Elements  | DAR on Loop 2              | Elements    |

|----------------------------|-----------|----------------------------|-------------|

| $R_{L_1 \to D_{Uodd}}(1)$  | {2}       | $R_{L_2 \to D_{Ueven}}(1)$ | {2}         |

| $W_{L_1 \to D_{Ueven}}(1)$ | {1}       | $W_{L_2 \to D_{Uodd}}(1)$  | {1}         |

| $R_{L_1 \to D_{Uodd}}(2)$  | {1}       | $R_{L_2 \to D_{Ueven}}(2)$ | {1}         |

| $W_{L_1 \to D_{Ueven}}(2)$ | {2}       | $W_{L_2 \to D_{Uodd}}(2)$  | {2}         |

| $R_{L_1 \to D_{Uodd}}(3)$  | {4}       | $R_{L_2 \to D_{Ueven}}(3)$ | {4}         |

| $W_{L_1 \to D_{Ueven}}(3)$ | {3}       | $W_{L_2 \to D_{Uodd}}(3)$  | {3}         |

| $R_{L_1 \to D_{Uodd}}(4)$  | $\{2,3\}$ | $R_{L_2 \to D_{Ueven}}(4)$ | {2,3}       |

| $W_{L_1 \to D_{Ueven}}(4)$ | {4}       | $W_{L_2 \to D_{Uodd}}(4)$  | {4}         |

| $R_{L_1 \to D_{Uodd}}(5)$  | $\{4,6\}$ | $R_{L_2 \to D_{Ueven}}(5)$ | $\{4,\!6\}$ |

| $W_{L_1 \to D_{Ueven}}(5)$ | {5}       | $W_{L_2 \to D_{Uodd}}(5)$  | {5}         |

| $R_{L_1 \to D_{Uodd}}(6)$  | {7}       | $R_{L_2 \to D_{Ueven}}(6)$ | {7}         |

| $W_{L_1 \to D_{Ueven}}(6)$ | {6}       | $W_{L_2 \to D_{Uodd}}(6)$  | {6}         |

| $R_{L_1 \to D_{Uodd}}(7)$  | {5,6}     | $R_{L_2 \to D_{Ueven}}(7)$ | $\{5,6\}$   |

| $W_{L_1 \to D_{Ueven}}(7)$ | {7}       | $W_{L_2 \to D_{Uodd}}(7)$  | {7}         |

are described by  $R_{L_l \to D_d}(\vec{i})$  and write relations by  $W_{L_l \to D_d}(\vec{i})$ . The access relations indicate which data locations in data space  $D_d$  that an iteration  $\vec{i} \in L_l$  accesses.

The DARs can be uninterpreted at compile-time, but must be known at runtime before the execution of the loop chain begins. This may be the case when the data access relation is dependent on input data, such as an unstructured mesh's topology or the placement of non-zeroes in a sparse matrix. Table 2.2 shows the data access relations for the example Jacobi solver and specific sparse matrix used in Figure 1.2

The data access relations are the critical piece of the loop chain abstraction. The DARs fully specify the data dependences between iterations of loops in the loop chain. The DARs can be used directly to determine if two iterations access the same data and therefore potentially have a data dependence or the DARS can be transformed into formal data dependency relations.

When specifying the access relations for a loop body, the programmer must include any data accesses that result in data dependences between iterations. This includes accesses that may be made from within procedures called from the loop body. Because the access relations are specified by the user, the granularity of the access relations can be user-determined. For

example, in a molecular dynamics application, the access relations may be from a loop iteration to a single directional component of the velocity vector of an atom, to any element of the velocity vector of an atom, or simply to the entire data structure for a particular atom, including velocity, force, position, etc. The programmer can also decide if a data access present in the code is relevant to the loop chain. For example, if a loop accesses data that remains invariant throughout the lifetime of the loop chain, the user may or may not choose to include those accesses. Some optimizations may benefit from that information, while others may not be impacted by the absence of that information.

## 2.3 Methods for Specifying Loop Chains

While it may be possible for a loop chain abstraction to be automatically extracted from source code by a compiler or other tool, in most cases a programmer will be required to specify all or part of the loop chain information. There are a variety of mechanisms that can be used to accomplish this task. These approaches range from an explicit description of the loop chain using an application programming interface or set of pragmas, to more implicit methods using domain specific languages or language extensions.

## 2.3.1 Application Programming Interfaces

As part of this dissertation, we wrote a complete application programming interface and C++ library called GROUT for specifying loop chains. The objects in the class library map directly to the elements in a loop chain definition. Figure 2.1 shows an example of using this API on the Jacobi solver code presented earlier in Figure 1.1. Line 2 creates a loop chain object. Line 6 instantiates an iteration space with a continuous range from 0 to numberOfRows-1 as its domain.

Lines 9 and 10 declare the data spaces for the UOdd and UEven arrays. The library supports several types of data access relations. The most general explicitly enumerates the data items associated with each iteration. Other access relations are provided for common, but more specialized, relations. The read data access relation declared on line 13 is of type

```

declare a loop chain

LoopChain chain0;

// create the iteration space

int numberOfRows = matrix->getNumRows();

ContiguousIterSpace iterAllRows(0,numberOfRows-1);

// create the data spaces

DataSpace UOdd(numberOfRows);

DataSpace UEven(numberOfRows);

Create the access relations

CSRAccessRelation relReadUOdd(iterAllRows, UOdd, matrix,

13

AccessType::READ);

Identity Access Relation relWrite UPrime (iter All Rows, UEven,

AccessType::WRITE);

17

// Assemble the loop

18

Loop loopUpdateUEven(bodyJacobiUpdateUEven, iterAllRows);

loopUpdateUEven.addAccessRelation(&relReadUOdd);

loopUpdateUEven.addAccessRelation(&relWriteUEven);

// add the loop to the loop chain

chain0.addLoop(loopUpdateUEven);

```

Figure 2.1: The kernel of a sparse Jacobi solver loop chained using the LoopChain API.

CSRAccessRelation and is an example of a specialized access relation that is derived from the non-zero pattern in the provided sparse matrix. The write relation on line 15 is a simple identity relation. These data access relations are attached to the loop loopUpdateUEven, which is then added to the loop chain on line 24.

Using the LoopChain API requires knowledge of loop chains and their definition. It requires 16 lines to fully specify the chain of two loops found in the Jacobi solver kernel. This approach to specifying loop chains is best used by experts or as the target of a tool, such as a source-to-source translator.

## 2.3.2 Pragmas

Pragmas can be used to annotate a program's source code, thereby delimiting the loop chain and providing information about data and iteration spaces and access relations. Figure 2.2 shows code taken from the Jacobi sparse matrix solver presented earlier in Figure 1.1. On lines 1 through 3, a hypothetical chain pragma, similar to OpenMP's pragmas, is shown. It declares the loop as part of a loop chain named chain 0. For this example, the proposed system would infer the iteration space from the loop bounds.

```

#pragma chain chain()\\

access( read, UEven, function(JA[p], IA[i] <= p < IA[i+1])) \\

access(write, UOdd, identity(i))

for (int i=0; i<numrows; i++) {

double diag = 1.0;

UEven[i] = 0.0;

for (int p=IA[i]; p < IA[i+1]; p++) {

int j = JA[p];

if (j=i) { diag = A[p]; }

else { UEven[i] += A[p] * UOdd[j]; }

}

UEven[i] = (F[i] - UEven[i]) / diag;

}

...</pre>

```

Figure 2.2: The kernel of a sparse Jacobi solver loop chained using hypothetical OpenMP style pragmas.

Lines 2 and 3 show how data access relations could be specified. Line 2 is a read relation on the U array. The relation itself might be a function declared using a function keyword describing the access as JA[p], where the value of p is given by the inequality IA[i] <= p < IA[i+1]. The identity write relation on the Uprime array is given on line 3. The second loop in the loop chain would be specified with a similar pragma.

Using a pragma-based approach may require only two pragmas to specify the loop chain in the Jacobi solver. However, the programmer must still be aware of the specifics of how loop chains are defined and the syntax for the pragmas might be considered cumbersome. Using pragmas also requires a compiler that can recognize and process the pragma appropriately. More research is necessary to determine the best pragma syntax that is both useable for programmers and feasible within existing compiler frameworks.

### 2.3.3 Domain Specific Languages

If loop chains are used in conjunction with an existing domain specific language (DSL), the task of specifying the needed loop information can be considerably simplified. Consider the OP2 (Oxford Parallel Library, version 2) [11] DSL. OP2 is designed for parallel computation on unstructured meshes. Its main feature is a parallel loop structure, op\_par\_loop. This parallel loop call takes as arguments an iteration space as well as some number of maps that go between iterations within the provided iteration space and elements in data struc-

```

program meshProgram

call op_decl_set (vertices, meshFile, "vertices")

{\bf call} \ {\tt op\_decl\_set} \ (\, {\tt cells} \ , \ {\tt meshFile} \ , \ "\, {\tt cells}" \, )

call op_decl_set (edges, meshFile, "edges")

6

call op_decl_dat (vertices, 6, vertexData, meshFile, "vertexData")

call op_decl_dat (edges, 6, edgeData, meshFile, "edgeData")

call op_decl_map (edges, vertices, 2, edges2Vertices, meshFile, "edges2Vertices")

10

call op_decl_map (cells, vertices, 2, cells2Vertices, meshFile, "cells2Vertices")

11

12

begin_loopchain ()

13

14

! loop over edges

15

call op_par_loop (edges, kernel1, &

16

op_arg_dat (temp, 1, edges2vertice, OP_INC), &

17

op_arg_dat (temp, 2, edges2vertice, OP_INC), &

18

op\_arg\_dat (x, -1, OP\_ID, OP\_READ))

19

20

!loop over cells

21

call op_par_loop (cells, kernel2, &

22

op_arg_dat (temp, 1, cells2vertices, OP_READ), &

23

op_arg_dat (temp, 2, cells2vertices, OP_READ), &

op_arg_dat (temp, 3, cells2vertices, OP_READ), &

op_arg_dat (res, -1, OP_ID, OP_WRITE))

end_loopchain ()

```

Figure 2.3: A kernel loop chained using OP2 loop constructs.

tures. The parallel loop mechanism works by calling the specified subroutine and passing it a single element of the iteration space. Additional arguments are retrieved from data sets using the iteration element and the data maps and passed to the subroutine.

Consider the example shown in Figure 2.3. The code shown here is two op2\_par\_loop calls that have been loop chained together. Lines 2 through 4 declare sets over which iteration can occur. These are the vertices, cells, and edges of the underlying mesh. Lines 6 and 7 identify data that is associated with vertices and edges, respectively. Lines 9 and 10 define mappings from edges to vertices or from cells to vertices.

If these OP2 DSL calls are considered from the vantage point of loop chains, analogies can be drawn. The op\_decl\_set calls of lines 2-4 are iteration space definitions. The op\_decl\_dat calls (lines 6-7) identify data spaces and the op\_decl\_map calls (lines 9-10) define data access relations. However, note that all these lines are present in OP2 code and are not specific to loop chaining. The only lines added for loop chains are lines 12 and 27, which declare the start and end of the loop chain.

Other DSLs, such as Chombo Fortran [21] for thermodynamics computations on structure meshes, also provide a similar level of ease of use for loop chaining.

## 2.4 Optimizations Enabled by Loop Chains

The loop chain's data access relations describe the data accesses that occur within each iteration of each loop in the chain. Based on that information, a compiler, runtime execution engine, or inspector can determine how best to schedule and place iteration execution as well as determine data layout and distribution.

For example, given a loop chain, data within sequential data spaces like arrays can be reordered to place data items such that they are stored in the order they are accessed. One algorithm for accomplishing this type of data reordering is the consecutive packing (CPACK) algorithm [28], which packs together data based on the first time it is accessed. Similarly, if iterations are grouped together into tiles or blocks, data can be reordered and packed such that all data items accessed by iterations within a tile are located in adjacent memory locations. These are just two examples of data reordering transformations that can be implemented using only data access relations and iteration orderings.

The loop chain abstraction also enables iteration reordering transformations, including those that mix iterations from different loops. One simple example is loop fusion [2], an optimization in which the *nth* iteration of two or more loops are either combined into a single loop iteration or are scheduled one after another. A simple examination of the iteration partial ordering can determine if this optimization is valid and a review of the data access relations can show if loop fusion would result in improved data locality.

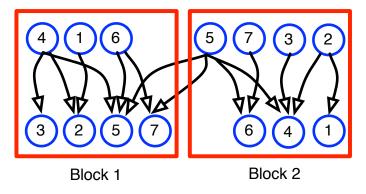

Full sparse tiling, introduced in Section 1.4, also reorders iterations across loops in an effort to improve locality. The seed iteration space is partitioned using a graph or hypergraph derived from the data access relations. These seed partitions are then grown to include iterations of other loops, once again under the direction of the data access relations. Figure 1.4 shows two schedules generated by full sparse tiling for the Jacobi solver example given in Figure 1.1.

Figure 2.4: A distributed memory work distribution across two nodes. Only element 5 of the Ueven vector, written by iteration 5 of the first loop, needs to be communicated from node 2 to node 1. All other data can be placed during initial data distribution.

A wide range of parallelization techniques can also be applied to loop chains. Different schedules or iteration groupings can be generated, depending on the type of parallel hardware being targeted. For example, a shared memory tiling can focus on memory locality and grouping the iterations based on in-core cache size.

Unlike shared memory parallelization, a distributed memory parallelization must consider internodal communication and data distribution. Fortunately, using data access relations, the data needed by each iteration assigned to a distributed memory node or address space is immediately known. Any data a node needs that are invariant over the life of the loop chain can be initially distributed using the appropriate communication. Since it is clear what data is altered during execution of the loop chain and by what node it is written, a communication schedule can be generated directly. This data being sent between nodes can then be aggregated into a small number of communication requests.

For example, in Figure 2.4, a distributed memory work distribution is shown for the Jacobi example of Figure 1.1. This schedule is easily derived from the partially ordered iterations of Figure 1.3. All communication between the two nodes is indicated by arrows crossing between nodes. Only data item UEven[4] needs to be sent between the nodes. Work by Basumallik et al. [7] takes an approach similar to this to aggregate and overlap communication and computation in a distributed memory system.

Parallelization approaches that involve work offload to a general purpose graphics processing unit (GPGPU) require much the same data distribution as traditional distributed memory parallelization. These approaches, however, may have additional requirements in terms of communication and synchronization between threads on the GPGPU. Because loop chains require that all iterations of a particular loop have no imposed ordering, no intraloop synchronization is required except in the case of reductions. Between loops, synchronization is only needed as determined by the partial ordering. This allows the computation to be broken into thread blocks that communicate via shared memory and only need to communicate via global memory rarely. Consider again Figure 2.4. The iterations assigned to node one could be executed within a thread block and those assigned to node two could be executed in another thread block. Each iteration in a given loop could be assigned to a different thread within the block. Between loops, the GPGPU would need to synchronize using hardware synchronization, such as is requested via Nvidia's CUDA language primative \_\_syncthreads(). The only communication needing global memory is the passing of UEven[4]. Synchronization between thread blocks requires scheduling assistance from the CPU to ensure that the thread block handling block two is not launched on the GPGPU until after block one has completed.

The examples given in this section are representative of the wide range of optimizations and code transformations that are enabled by loop chains. Shared memory, distributed memory, and GPGPU parallelization methods are all facilitated by using the loop chain abstraction. Data and iteration reordering transformations also can be expressed within the context of loop chains.

# 2.5 Examples of Loop Chains Present in Existing Scientific Codes

Commonly, data in scientific applications is organized as structured or unstructured meshes, grids, or geometric subdivisions, such as boxes, of a larger three dimensional space.

These subdivisions may come from finite element or finite volume approaches to solving partial differential equations.

In order to promote sustainability and reusability of code, scientific applications are often architected as a series of passes over some data structures. Each pass applies a particular function or computes one type of value, e.g. temperature, pressure, velocity, position, and so forth. Data from one pass often feeds the next pass through a producer-consumer relationship. Multiple passes may also be the result of applying a function to each of multiple dimensions, such as the force in the x, y, and z dimensions. Rather than combine passes, the passes are kept distinct so that the code can be reused and so that the code does not become intertangled [37, 21].

One example of this code structure is given in Figure 2.5, which shows the central kernel of a molecular dynamics benchmark. Here a sequence of three loops is found inside an outer time step loop.

Figure 2.6 shows another example of a loop chain. This example is drawn from the *airfoil* computational fluid dynamics test program [10, 11]. A series of three loops in enclosed in an outer time step loop. The inner loops compute the change in area of a mesh cell, the flux residual for each edge, and the flow through each cell, respectively.

Even though this example is drawn from an entirely different scientific domain and is solving a distinctly different problem, the overarching design of the code very closely resembles the molecular dynamics simulation given in Figure 2.5. Other similar occurrences of series of loops can be found in thermodynamics simulations [21].

In some cases, a series of loops is the result of unrolling a loop by some factor. What was previously one loop becomes a series of related loops after unrolling. This was seen in the case of the ping-pong version of the Jacobi solver seen in Figure 1.1. In this code, the main convergence loop has been unrolled by a factor of two, resulting in a series of two sequential loops. These unrolled loops form a loop chain. Greater unrolling factors generate progressively longer loop chains.

```

for (int timestep = 0; timestep < maxTimesteps; ++timestep)</pre>

2

3

// do the per-atom position updates

4

for (int i=0; i < numAtoms; i++)

5

6

x(i) = x(i) + vhx(i) + fx(i);

7

y(i) = y(i) + vhy(i) + fy(i);

z(i) = z(i) + vhz(i) + fz(i);

9

10

// clear the force vector

11

fx(i) = 0.0;

12

fy(i) = 0.0;

13

fz(i) = 0.0;

14

15

16

// do the per-interaction force updates

for (int ii = 0; ii < ninter; ii + +)

17

18

19

int i = inter1(ii);

20

int j = inter2(ii);

21

22

// compute the force between interacting atoms

23

forcex = f(x(i), x(j))

forcey = f(y(i), y(j))

24

25

forcez = f(z(i), z(j))

26

27

fx(i) += forcex;

28

fy(i) += forcey;

29

fz(i) += forcez;

30

31

fx(j) = forcex;

32

fy(j) -= forcey;

33

fz(j) = forcez;

34

35

36

// do the per-atom velocity updates

37

for (int i=0; i < numAtoms; i++)

38

{

39

40

vhx(i) += fx(i);

41

vhy(i) += fy(i);

42

vhz(i) += fz(i);

43

44

45

}

```

Figure 2.5: The kernel of the MolDyn molecular dynamics benchmark. Within the outer time step loop is a sequence of three inner loops. They compute the position, interactive force, and velocity of atoms in the simulation, respectively, and form a classic loop chain.

```

int edgesToCells[numEdges][2]; // maps from edge to cells on either side

for (int timestep=0; timestep < maxTimesteps; ++timestep)</pre>

6

7

// for each cell, compute the change in area based on flow q

8

for (int cell=0; cell < numCells; ++cell)

10

updateArea(q[cell], area_dt[cell]);

11

12

/\!/ for each edge, update the flux residual for cells on either side of edge

13

for (int edge=0; edge < numEdges; ++edge)

14

15

calcFluxResidual(q[edges2Cells[0]]\;,\;\;q[edges2Cells[1]]\;,

16

17

18

19

20

// update the flow field per cell based on the area and residual

21

22

(int cell=0; cell < numCells; ++cell)

23

updateFlowField(area_dt[cell], residual[cell], q[cell]);

24

25

26

27

```

Figure 2.6: The kernel of the *airfoil* computational fluid dynamics benchmark. Within the outer time step loop is a sequence of three inner loops. They compute the change in area, flux residual, and flow field, respectively, and form a classic loop chain.

# 2.6 Prior Work Related to Loop Chains

The loop chaining abstraction complements the application of previously developed automated code transformation strategies. The abstraction promises to enable the same level of performance as manual approaches, while remaining portable to new architectures and not requiring users to define explicit tasks. This section describes work previously done to expose asynchronous parallelism by scheduling manually defined tasks, scheduling automatically discovered tasks, and by rewriting existing algorithms to avoid communication.

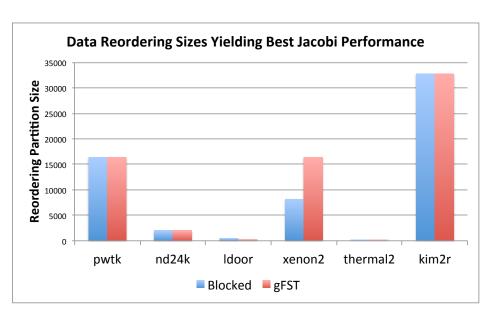

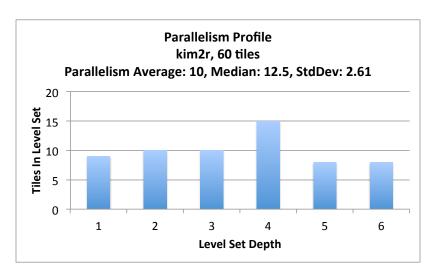

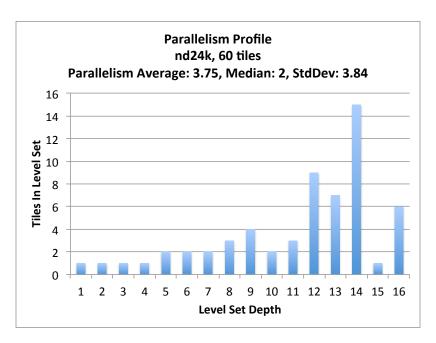

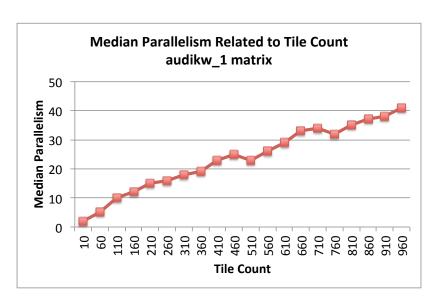

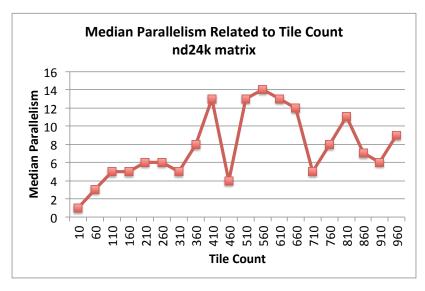

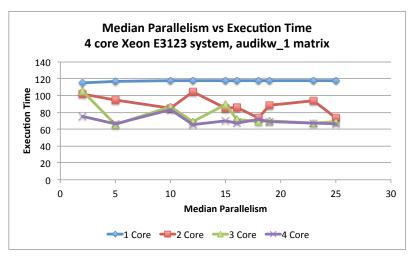

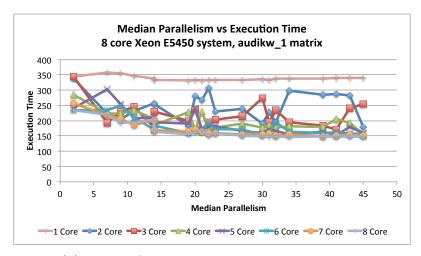

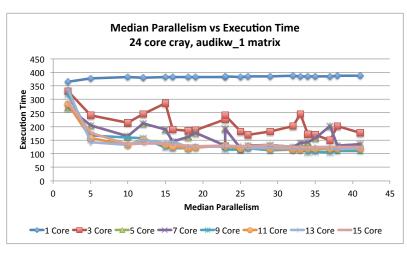

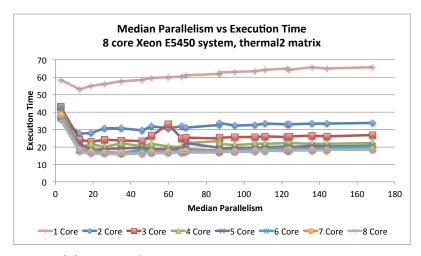

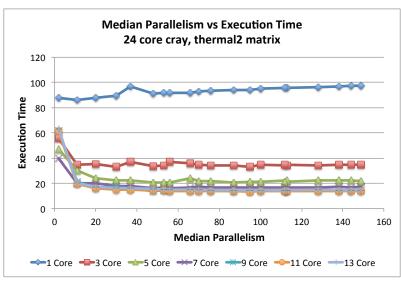

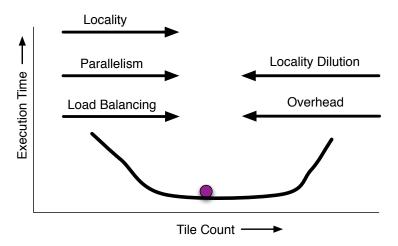

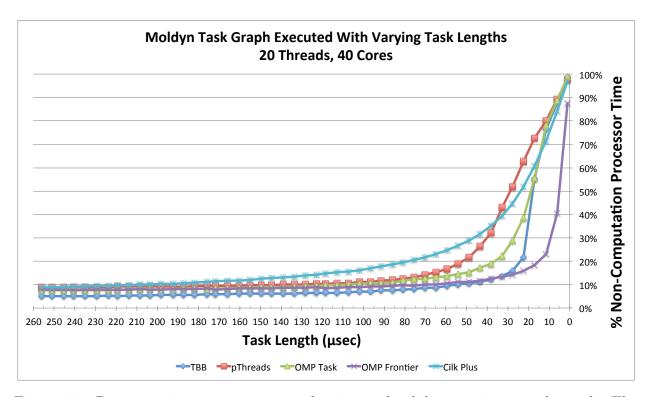

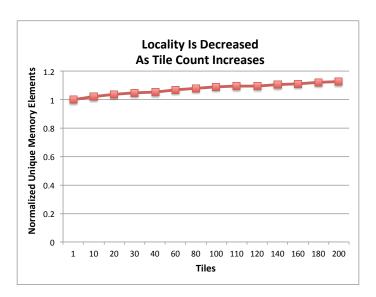

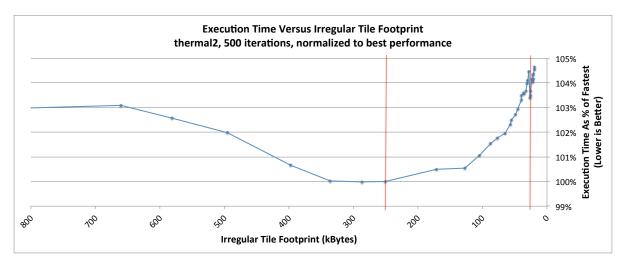

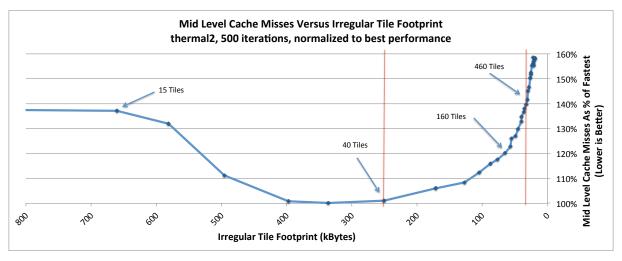

# 2.6.1 Programming Models Using User Defined Tasks