#### **DISSERTATION**

# DESIGN METHODOLOGY AND PRODUCTIVITY IMPROVEMENT IN HIGH SPEED VLSI CIRCUITS

# Submitted By

#### KM Mozammel Hossain

Department of Electrical and Computer Engineering

In partial fulfillment of the requirements

For the Degree of Doctor of Philosophy

Colorado State University

Fort Collins, Colorado

Spring 2017

**Doctoral Committee:**

Advisor: Thomas W Chen

Yashwant Malaiya Sudeep Pasricha Ali Pezeshki Copyright by Mozammel Hossain 2017

All Rights Reserved

#### **ABSTRACT**

# DESIGN METHODOLOGY AND PRODUCTIVITY IMPROVEMENT IN HIGH SPEED VLSI CIRCUITS

Recent changes in the technology market demand faster turnaround of the design, and as a result, designers struggle to meet performance requirements under prohibitively expensive non-recurring engineering (NRE) costs. Increasing costs for the design, validation, and time to market are some of the most pressing issues for next generation microprocessor systems. Custom versus synthesis VLSI circuit design has been a lively debate for the last decade. However, the ever-increasing cost of designs in large-scale projects is becoming a bottleneck to the industry, thus, the wind is blowing strongly in favor of synthesis, especially when the modern synthesis engines are becoming more and more sophisticated in closing timing, completing routings, avoiding congestions and better interface with all the backend tools. Custom design advocates will argue that the last pico-second and milli-watts cannot be left on the table, but the reality is, they need to get over this mentality in favor of cost, time to market, and ability to adopt the last minute-change of the design.

As the industry moves into the next generation of microprocessor design, it faces growing complexity in device scaling, supporting algorithm, and time to market. The need for customization has never been greater to address specific needs for customers. Building a complex microprocessor system is complicated and time consuming. Thus, circuit designers need to face the reality and move forward for more automation in the design cycles. While the past generations of microprocessors had more custom circuit design to meet tighter cycle time

battle, more startups and IC companies are trying to design by moving towards common synthesizable design methodology, and in most cases, sacrificing the desired speed in favor of new functionality.

Needless to say, improving the synthesis methodology as an alternative to the custom circuit design is gaining high momentum in the industry because the custom design most often needs hand crafted schematics and layout design which are overwhelmingly time consuming requiring as high as 2-4 times development time to the synthesis. However, the key point is to stay within a similar area and power budget, and yet cut significant time to development cycle of the design. Study shows, with the help of advanced Electronic Design Automation (EDA) tool capabilities i.e. advanced algorithm for timing, power and congestion-mitigation, the synthesis-based-design is increasing by about 30% relative to its predecessor.

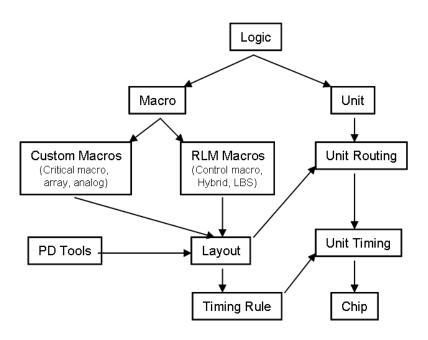

With the goal of mitigating the rising cost of designing custom macros and eliminating the limitation of the usages of smaller Random Logic Macros (RLM), in this dissertation, it is intended to work on a methodology and algorithm development that will enable the industry to synthesize custom and RLM macros into bigger macro, Multi-Million Logic Gate Synthesis (MMLGS), to improve the Physical Design (PD) resource efficiency. Additionally, MMLGS methodology most often requires embedded IP or custom components, which may require different power supply rail(s) and (or) sync-async clocking interface(s). One of the popular timing methodologies is to share positive slack across the latches to ease the timing burden from one cycle to another, thereby closing time-challenged and architecturally critical paths. Similarly, multi-power supplies are used in design to either dynamically control part of the circuits or statically isolate a portion of the logic to different power islands to control the total power consumptions of the chip. In a custom circuit design, designers carefully hand craft gates to

support these multi-clock and multi-power domains, satisfying the timing and methodology requirements. However, in a high-speed synthesis design environment, designers struggle to make sure multi-clock and multi-power interfaces are designed, placed, connected, and timed correctly. Identifying and applying the proper timing constraints such as "no cycle stealing" at synchronous and asynchronous (sync-async) domain interfaces in synthesis, unit, and chip timing, are of the essence. Even though some of these concepts are available now and were used in the past but they have very limited application to the custom design methodology only.

As the synthesis methodology for MMLGS is being developed, work in this dissertation will also include developing algorithms and design methodologies for multi-power and multi-clock domains to take advantage of slack sharing across all hierarchies of the chip design. The developed algorithm and methodology will: 1) improve physical design resource efficiency; 2) improve performance by sharing unused slacks efficiently at appropriate design hierarchies; 3) improve logic optimization by collapsing smaller macro boundaries; and 4) enable correct placement and connectivity of logic-gates in multi-power domain. Upon successful implementation of the design methodology approach for MMLGS with multi-power and multi-clock, these designs need to be functionally verified for different input stimuli at different frequencies. At the same time, the design must comply with all backend tools such as noise, electro-migration, timing, and of course all PD verification tools such as DRC, LVS, and YLD etc. to demonstrate electrical and physical feasibility of the design.

Overall, a synthesis based physical design methodology using soft hierarchy, interior pin placement, pre-placing critical logic, post-routing techniques, has been developed and proposed in this dissertation. The effectiveness of the proposed design methodology is illustrated using a very time and area challenged unit, the level-2 cache (L2 cache) unit. Additional synthesis based

physical design algorithms and methodologies have been developed for level translators at multivoltage domains and slack sharing at sync-async interface paths at all level of PD hierarchies. Proposed design methodologies show how slack sharing can be an advantage to ease timing, and yet avoid potential meta-stability in the circuit. The developed methodology can save significant number of physical design resources because millions of gates can be packed in a synthesizable macro even in multi-clock and power domain instead of designing those macros individually in high-cost design flow. By adopting the proposed MMLGS methodology along with multi-voltage and clock approach in synthesis and timing methodology, development costs can be cut by about 50%, which is substantially significant PD resource savings in high-cost VLSI circuit design.

#### **ACKNOWLEDGEMENTS**

As much, and perhaps more than, this dissertation represents my personal abilities, it represents how lucky I am to be surrounded by incredible people who guided me, provided a shoulder to lean on, and examples to live by. First and foremost, I would like to thank Prof. Tom Chen, my advisor, for his guidance, encouragement, and suggestions during my research work with him. Prof. Chen provided me with all the tools necessary to complete my research within a short period of time. I am ever grateful to Prof. Chen for his commitment to excellence in research and the opportunity given to me to complete my dream! My heartfelt thanks go to all my committee members, Prof. Yashwant Malaiya, Dr. Sudeep Pasricha, and Dr. Ali Pezeshki for their help in shaping up my research with their invaluable critiques and suggestions.

IBM is a wonderful place to work, with many wonderful mind and people, many of whom have become my friends, colleagues, and mentors along the way. A great and special thank to my consulting advisor, Dr. Vikas Agarwal. Over the years, he enabled me to think and look beyond the scope of the research topic and provided direction with his thoughts and ideas. An enormous thank you and gratitude is also sent to Joshua Friedrich, my mentor, for his help and guidance from the day one here at IBM. I am not shy to say that I would not be where I am today without his help and the opportunities given to me. Furthermore, I am grateful to a good friend of mine, John Badar, for his help, honest feedback on my dissertation topics, and helping me to stay positive all the time. I wish to extend many thanks to my managers Sam Thomas, Mike Carlson, Gilbert Prince, and all my colleagues for their day-to-day help and providing me a shoulder to lean on when it is needed the most.

When I look at my life, I go back all the way to my school life and remember very important contributions that shaped up my life. My elementary school teacher, Abul Hossain, and high school teachers Shushanta K. Roy, Abdul Baten Selim, Abdul Gafur and Fazlul Haque, all played a crucial role and helped me to grow and think out of the box at very early stages of my life. I would like to extend my sincere gratitude to these wonderful teachers of my life.

I grew up with amazing brothers and sisters, all of whom provided me unparalleled love and affection that I cherish all the time. Mosharrof Hossain, Monzed Khan, Mokbul Hossain, and Masud Khan are not only my brothers, but also my dearest friends. Their wives and children are amazing family members who comforted me with their affection in my bad and good days. I am truly honored and grateful for such a wonderful family that is second to none. I would also like to thank my wife's parents, Mr. Shamsul Haque and Mrs. Rabeya Begum, who supported our decision to live on the other side of the world, even though I know how tough this was for them, and for making constant trips to visit and help us during our need.

I am in debt to my parents for their unconditional love, sacrifices, and prayers throughout my life. When I put my Ph.D. work on hold, I made my father upset the most. My father flatly told me, "I did not send you to the USA for job, I sent you for Doctoral Degree". It is amazing how his favorite quote, "Try and Try, Again Try, You Will Succeed," influenced me from my childhood until now. I am certain you, my dearest friend, mentor, and dad, looking from the heaven and resting in peace, knowing that I never gave up and fell short to fulfill your dream!

Finally, my greatest thanks are to my sons, Mushroor and Mainur, and my daughter, Samia, who joined us along the way and made our lives so wonderful. You all are the best gift of our life! And to top it all, Sharmin, my love, there are not enough words to express my love and gratitude to you—this Ph.D. is as much yours as it is mine!!

#### **DEDICATION**

To my late mother, beautiful wife Sharmin, amazing sons Mushroor and Mainur, wonderful daughter Samia, all my brothers and sisters, especially my brother Mokbul Hossain

and

dedicated with love to the memory of my mentor, best friend and father: Abdul Latif Khan.

# TABLE OF CONTENTS

| ABSTRAC'   | Т       |           |                                        | ii    |

|------------|---------|-----------|----------------------------------------|-------|

| ACKNOWI    | LEDGEN  | MENTS     | ······································ | vi    |

| DEDICATION | NC      |           |                                        | viii  |

| LIST OF TA | ABLES . |           |                                        | xiv   |

| LIST OF FI | GURES   |           |                                        | XV    |

| LIST OF PR | ROPOSE  | D ALG     | ORITHMS                                | xviii |

| Chapter 1  | Introd  | duction . |                                        | 1     |

| Chapter 2  | Over    | view of 1 | Existing Synthesis Methodology         | 7     |

|            | 2.1     | Synth     | esis in Today's VLSI Design            | 8     |

|            | 2.2     | Input     | to Synthesis Tools                     | 10    |

|            |         | 2.2.1     | Register Transfer Level (RTL)          | 11    |

|            |         | 2.2.2     | Assertions                             | 12    |

|            |         | 2.2.3     | Macro Physical Abstract                | 14    |

|            |         | 2.2.4     | Control Files                          | 15    |

|            | 2.3     | Typica    | al Synthesis Flow                      | 15    |

|            |         | 2.3.1     | Logic Re-structuring                   | 17    |

|            |         | 2.3.2     | Technology Mapping                     | 19    |

|           |      | 2.3.3 Latch Clustering and LCB Cloning         | 25 |

|-----------|------|------------------------------------------------|----|

|           |      | 2.3.4 Control Logic Structure                  | 26 |

|           |      | 2.3.5 Pre-Placing Logic                        | 28 |

|           | 2.4  | Review of Quality of Data                      | 28 |

|           | 2.5  | Synthesis Output                               | 29 |

|           |      | 2.5.1 Major Output Files                       | 30 |

|           | 2.6  | Early Mode Padding (EMPAD)                     | 33 |

|           | 2.7  | Routing                                        | 34 |

|           | 2.8  | Post Routing Optimizations                     | 37 |

|           | 2.9  | Summary                                        | 39 |

| Chapter 3 | Draw | backs of the Existing Synthesis Flows          | 40 |

|           | 3.1  | Physical Design Resource Limitation            | 43 |

|           | 3.2  | <u>T</u> urn <u>A</u> round <u>T</u> ime (TAT) | 43 |

|           | 3.3  | Timing Optimization                            | 44 |

|           | 3.4  | Power and Area Optimization                    | 45 |

|           | 3.5  | Sync-Async Interface in Synthesis              | 46 |

|           | 3.6  | Multi-Power Domain in Synthesis                | 47 |

|           | 3.7  | Summary                                        | 48 |

| Chapter 4 | Circu | iit Desig | n of Common Library for Research Experiment                    | 50 |

|-----------|-------|-----------|----------------------------------------------------------------|----|

|           | 4.1   | Libra     | ry Cells                                                       | 50 |

|           | 4.2   | Latch     | Design                                                         | 51 |

|           | 4.3   | Array     | Design                                                         | 52 |

|           | 4.4   | Sync-     | Async Latch Pack                                               | 53 |

| Chapter 5 | Prop  | osed MM   | ALGS and Timing Methodology                                    | 56 |

|           | 5.1   | Introd    | uction                                                         | 56 |

|           | 5.2   | Multi     | -Million Logic Gate Synthesis (MMLGS) Methodology              | 57 |

|           |       | 5.2.1     | Enhancement to the Existing Synthesis for MMLGS                | 59 |

|           |       |           | 5.2.1.1 Soft Hierarchy Methodology & Algorithm                 | 60 |

|           |       |           | 5.2.1.2 Multi-VT insertions & Algorithm                        | 62 |

|           |       |           | 5.2.1.3 Internal Pin, Pre-Placing Critical Logic and Algorithm | 63 |

|           |       | 5.2.2     | Proposed Multi-Power Design Methodology for MMLGS              | 66 |

|           |       |           | 5.2.2.1 Parameters in Synthesis for Multi-Power Design         | 67 |

|           |       |           | 5.2.2.2 Proposed Algorithm for Multi-Power Synthesis           | 70 |

|           |       | 5.2.3     | Proposed Timing Methodology for Sync-Async Interface           | 73 |

|           | 5.3   | Conge     | estion Analysis in MMLGS                                       | 78 |

|           | 5 4   | Noise     | Analysis in MMLGS                                              | 80 |

|              | 5.5  | Electromigration in MMLGS                                     | 81    |

|--------------|------|---------------------------------------------------------------|-------|

|              | 5.6  | Bug Fixes and Design Change in MMLGS                          | 82    |

| Chapter 6    | Exp  | erimental Results                                             | 83    |

|              | 6.1  | Multi-Million Logic Gate Synthesis (MMLGS) Methodology        | 83    |

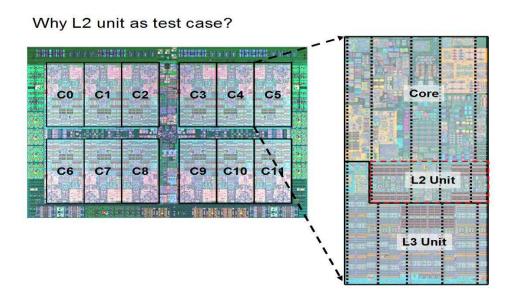

|              |      | 6.1.1 Experiment Setup Using the L2 Cache Unit in IBM's Power | r8 83 |

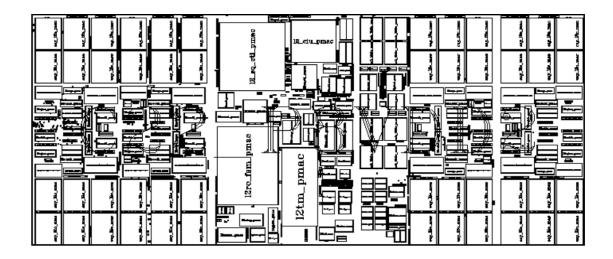

|              |      | 6.1.2 Placement of Macros                                     | 85    |

|              |      | 6.1.3 Power Routing                                           | 86    |

|              |      | 6.1.4 Clock Routing                                           | 86    |

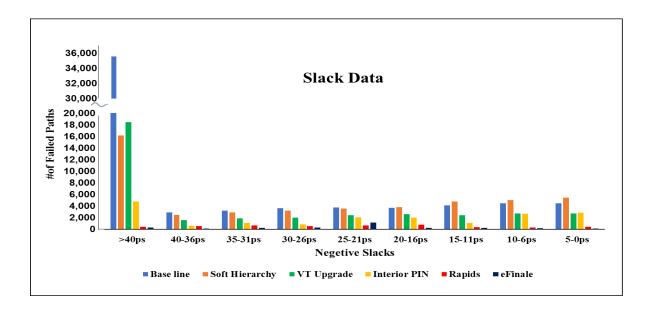

|              |      | 6.1.5 Timing Results                                          | 88    |

|              |      | 6.1.6 Silicon Area Results                                    | 90    |

|              |      | 6.1.7 Power Data                                              | 91    |

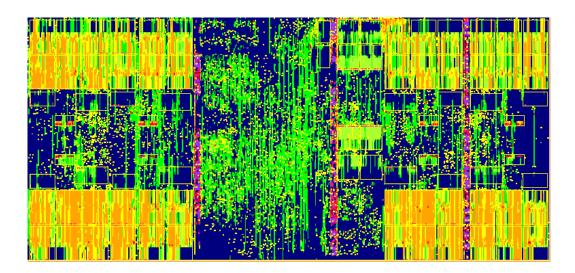

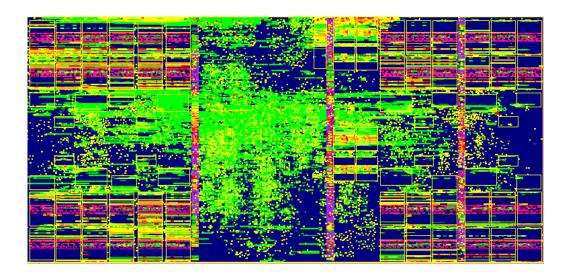

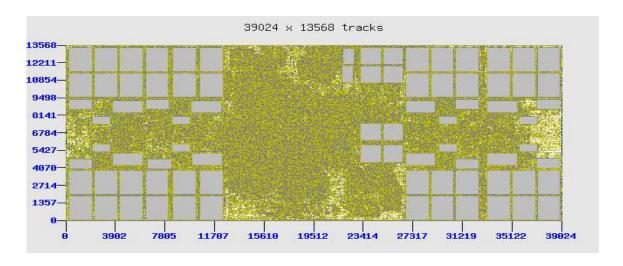

|              |      | 6.1.8 Results on Wire Usages                                  | 92    |

|              | 6.2  | Multi-Voltage Synthesis for MMLGS                             | 96    |

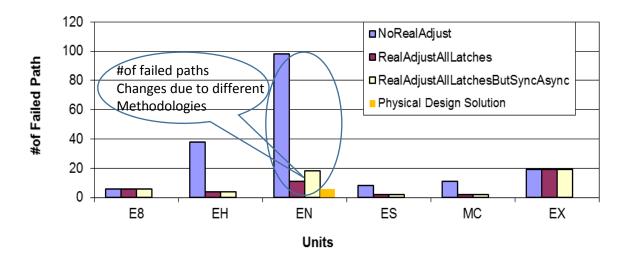

|              | 6.3  | Sync-Async Timing Methodology                                 | 98    |

| Chapter 7    | Conc | lusions and Future Work                                       | 101   |

| Bibliography | у    |                                                               | 104   |

| Appendix |     |                                       | 116 |

|----------|-----|---------------------------------------|-----|

|          | A.1 | RodRunner Library                     | 116 |

|          | A.2 | Congestion Analysis                   | 116 |

|          |     | A2.1 Vertical Wiring Congestion       | 117 |

|          |     | A2.2 Horizontal Wiring Congestion     | 118 |

|          | A.3 | Routing Analysis                      | 119 |

|          | A.4 | Distribution of Gate Array (GA) Cells | 122 |

|          | A.5 | Slack Distribution                    |     |

|          | A.6 | Post Routing Statistical Data         | 123 |

# LIST OF TABLES

| Table 2.1 | Example of PIS assertions                                      | 13 |

|-----------|----------------------------------------------------------------|----|

| Table 2.2 | Example of POS for assertions                                  | 13 |

| Table 2.3 | Example of ETA assertions                                      | 14 |

| Table 2.4 | Post processing tool to fix timing violation                   | 38 |

| Table 6.1 | Wire usages in L2 cache unit routing                           | 93 |

| Table 6.2 | Physical design resource comparison for L2 cache               | 95 |

| Table 6.3 | Physical design resource comparison for a typical macro design | 98 |

# LIST OF FIGURES

| Figure 1.1   | Microprocessor road map of IBM, Intel and AMD        | 2  |

|--------------|------------------------------------------------------|----|

| Figure 1.2   | IBM's POWER microprocessor delivery roadmap          | 3  |

| Figure 1.3   | Intel's technology roadmap for microprocessor design | 3  |

| Figure 2.1   | Microprocessor trend data for 35 years               | 7  |

| Figure 2.2   | Macro customization vs design effort                 | 9  |

| Figure 2.3   | IBM's L2 cache macro design methodology trend        | 10 |

| Figure 2.4   | An example of high level function                    | 12 |

| Figure 2.5   | A typical synthesis flow                             | 16 |

| Figure 2.6.1 | Logic transduction                                   | 17 |

| Figure 2.6.2 | Logic cube factoring                                 | 18 |

| Figure 2.6.3 | Common factoring                                     | 18 |

| Figure 2.6.4 | Logic merging                                        | 18 |

| Figure 2.7   | Technology mapping                                   | 19 |

| Figure 2.8   | Gate placement optimization                          | 21 |

| Figure 2.9   | Slack optimization                                   | 22 |

| Figure 2.10  | Latch and LCB placement flow                         | 23 |

| Figure 2.11  | Initial latch and LCB placement                      | 23 |

| Figure 2.12  | Final latch and LCB placement                        | 24 |

| Figure 2.13  | Latch clustering and LCB cloning                     | 26 |

| Figure 2.14  | Logic structure control.                             | 27 |

| Figure 2.15  | Example of worse slack plot in synthesis             | 31 |

| Figure 2.16  | Example of timing path in synthesis                  | 32 |

| Figure 2.17  | Example of early mode padding (EMPAD)                | 33 |

| Figure 2.18  | Input and output of routing in synthesis             | 36 |

| Figure 2.19  | Routing flow                                         | 36 |

| Figure 2.20  | Routed design                                        | 37 |

| Figure 2.21  | Bad routing and fix after post-processing            | 39 |

| Figure 3.1  | Design methodology for synthesized macro                                  | . 41 |

|-------------|---------------------------------------------------------------------------|------|

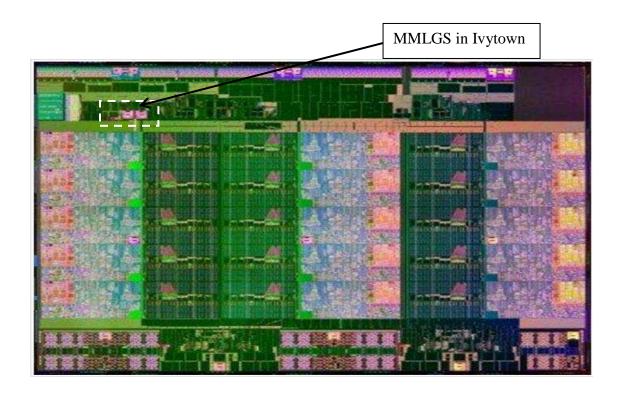

| Figure 3.2  | MMLGS usages in the industry (Intel's Ivytown Microprocessor)             | 42   |

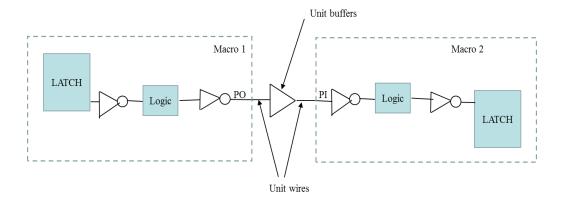

| Figure 3.3  | Unoptimized macros at unit                                                | 44   |

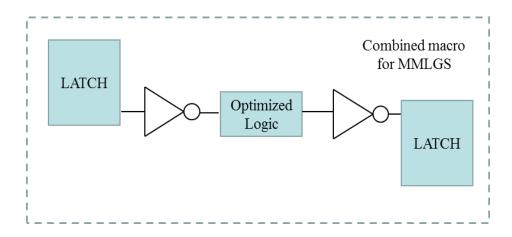

| Figure 3.4  | Optimized macro with proposed MMLGS methodology                           | . 45 |

| Figure 3.5  | Example of timing slack in 2 cycle                                        | 46   |

| Figure 3.6  | Example of slack sharing                                                  | 46   |

| Figure 4.1  | Master-slave latch                                                        | . 51 |

| Figure 4.2  | Timing diagram of master-slave latch                                      | . 52 |

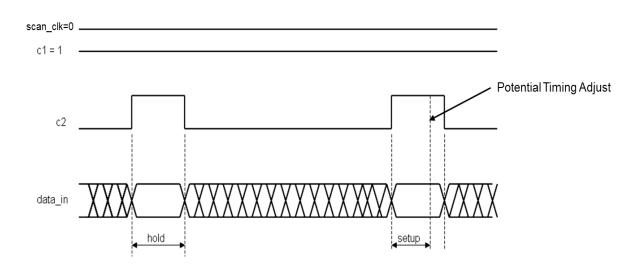

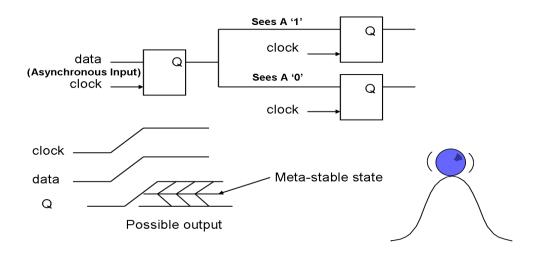

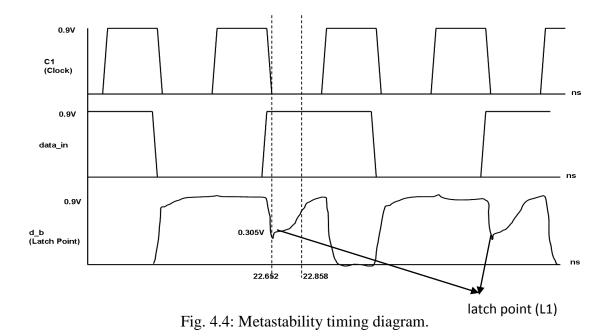

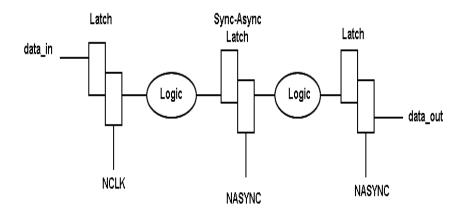

| Figure 4.3  | Metastability example                                                     | 54   |

| Figure 4.4  | Metastability timing diagram                                              | 54   |

| Figure 4.5  | Sync-async latch pack                                                     | 55   |

| Figure 5.1  | High level physical design flow in VLSI circuits                          | 56   |

| Figure 5.2  | Enhanced synthesis flow for MMLGS                                         | . 59 |

| Figure 5.3  | Soft hierarchy example in synthesis flow                                  | . 61 |

| Figure 5.4  | A sample placement file                                                   | 65   |

| Figure 5.5  | Example of a generic "Level Translator" (LT)                              | 66   |

| Figure 5.6  | "Level Translator" (LT) is expected to drive gate with "VIO"              | . 67 |

| Figure 5.7  | Example of placement file for LT                                          | 69   |

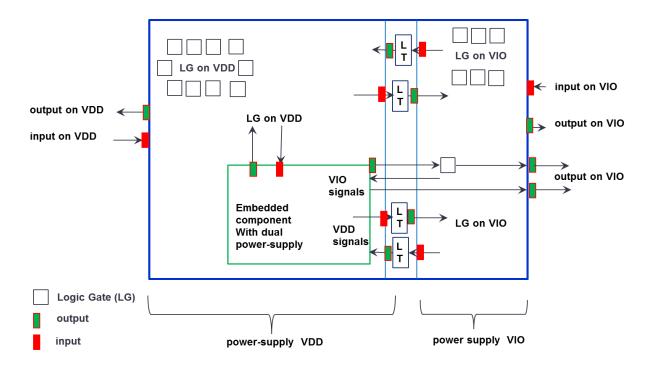

| Figure 5.8  | Expected placement and connectivity of component in multi-power synthesis | 70   |

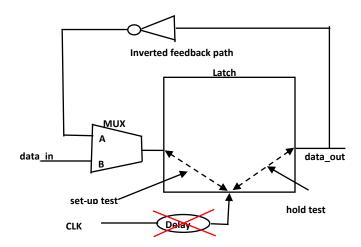

| Figure 5.9  | Latch with feedback path                                                  | 74   |

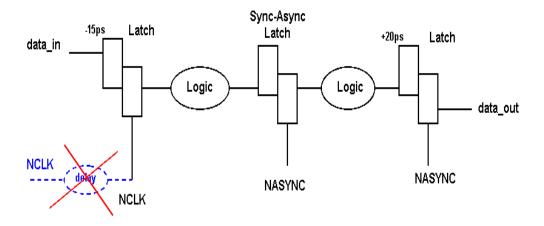

| Figure 5.10 | No auto REAL adjust at sync-async interface                               | 75   |

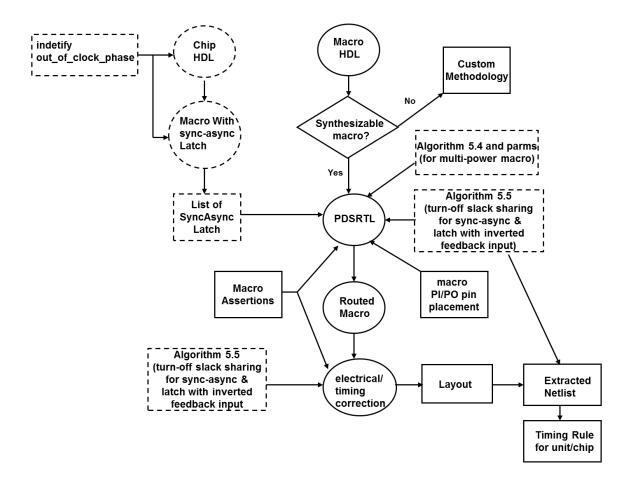

| Figure 5.11 | Proposed design flow at sync-async interface and multi-power domain paths | 78   |

| Figure 5.12 | Local congestion problem in synthesis                                     | 79   |

| Figure 6.1  | IBM's P8 microprocessor                                                   | 83   |

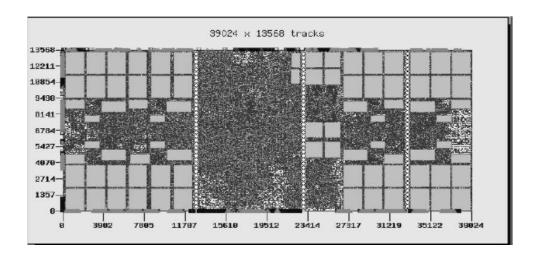

| Figure 6.2  | Floor-plan of test case: L2 cache unit                                    | 85   |

| Figure 6.3  | Slack buckets for synthesis methodology                                   | 88   |

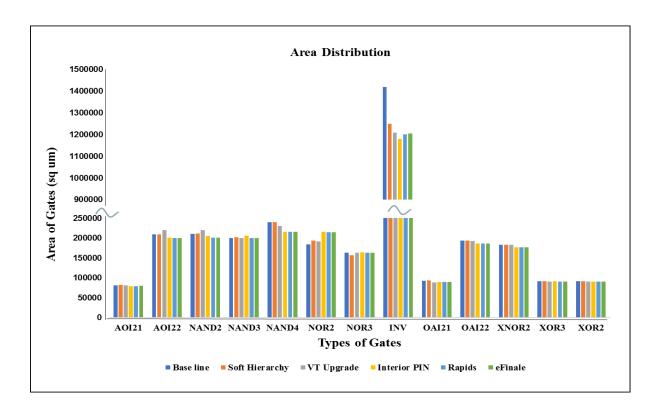

| Figure 6.4  | Area distribution of logical gates                                        | 90   |

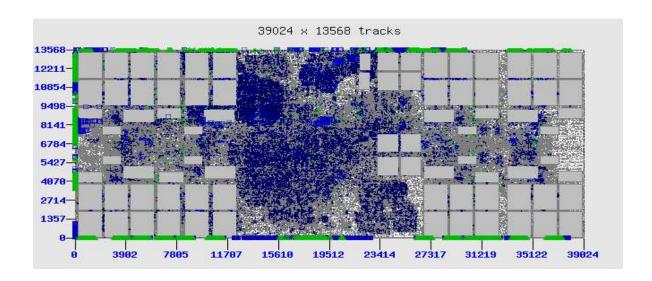

| Figure 6.5  | Placed gates in L2 unit with synthesis methodology                        | . 94 |

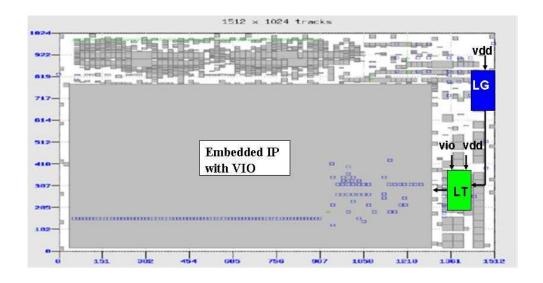

| Figure 6.6  | Use of level shifter in MMLGS                                             | . 96 |

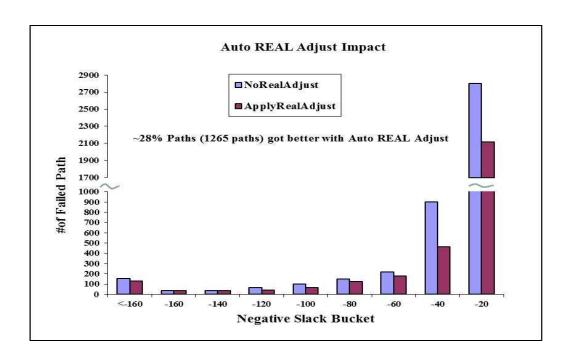

| Figure 6.7  | Distribution of negative paths with and without "Auto REAL Adjust"        | . 99 |

| Figure 6.8 | Slack distribution with/without "Auto REAL Adjust | )() |

|------------|---------------------------------------------------|-----|

| Figure A.1 | Vertical wiring solution                          | 7   |

| Figure A.2 | Horizontal wiring solution                        | 8   |

| Figure A.3 | Routing iteration to fix design violation         | 20  |

| Figure A.4 | Congestion data in L2 cache unit                  | 21  |

| Figure A.5 | Distribution of GA cell after synthesis           | 22  |

| Figure A.6 | Distribution of negative slack in synthesis       | :3  |

| Figure A.7 | Post routing tool improvement statistics          | 24  |

# LIST OF PROPOSED ALGORITHMS

| Algorithm 5.1 | pseudo code for soft-hierarchy during synthesis | 60 |

|---------------|-------------------------------------------------|----|

| Algorithm 5.2 | pseudo code to upgrade Vt                       | 63 |

| Algorithm 5.3 | pseudo code for interior pin                    | 64 |

| Algorithm 5.4 | pseudo code to connect multi-power              | 71 |

| Algorithm 5.5 | pseudo code for proposed timing methodology     | 76 |

# Chapter 1

#### Introduction

In high-speed microprocessor design, the most concerning issue is product design and verification costs. One direction that industry has attempted, with the goal of mitigating the rising costs of per-application designs, is to move toward with synthesis instead of custom design, because in custom design, major re-engineering is required when moving from one technology/design point to the next. Thus, the focus is to find a design methodology to shorten the design cycle and lower development costs.

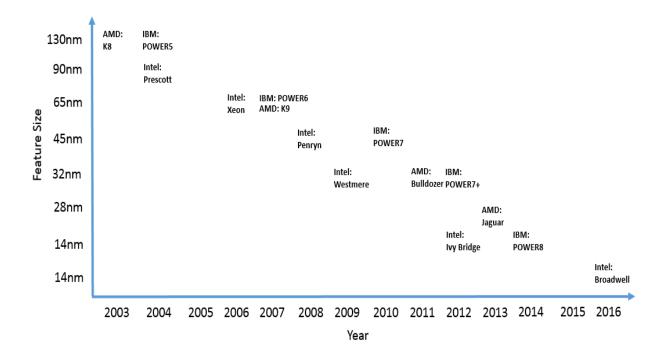

In the past 20 years, microprocessors technology has experienced improvements circuit integration and microprocessor throughput. The technology has rapidly due to transistor speed, energy scaling and core micro architecture advances powered by Moore's law. In every generation (two years), transistor density has doubled as their dimensions have been reduced by 30% (shrinking their area 50%), and circuits have become 40% faster increasing the whole system performance [1]. However, due to the battery capacity and chip reliability (heat dissipation limits), power consumption has been one of the key limiting factors for performance scaling in the single-core microprocessor technology. In the past decade, multi-core microprocessors have become the major design trend. Limits in instruction level parallelism (ILP) and power dissipation constraints have triggered the high-performance microprocessor roadmap to enter the multi-core era, starting from the high-end server processors and moving to the low-end hand-held mobile device processors. A multi-core micro architecture provided an effective alternative to improve throughput performance of parallel programs while keeping power consumption under the control. To improve efficiency, single-thread performance was sacrificed and instead multiple cores were joined on a single chip when more transistors became available [2]. The more threads accommodated in the application set, the more efficient the processors became [3-4]. Recently the typical pattern among multi-core CPU products is to keep the number of cores constant within a generation and double the number of transistors within each core [5]. By exploiting Moore's Law to replicate cores, multi-core architectures increased computational performance. However, there is no real benefit if the software has no parallelism [6]. Fig. 1.1 is an illustration of the microprocessor roadmap for industry leaders (IBM, Intel and AMD) from technology to technology over the past 12 years in order to cope with increasing demand for on and off chip performance including new functions within reasonable power and manufacturing cost.

Fig. 1.1: Microprocessor road map of IBM, Intel and AMD [7-9].

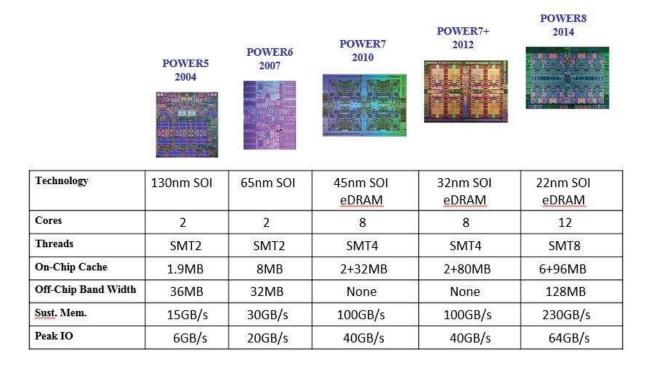

Fig. 1.2: IBM's POWER microprocessor delivery roadmap [7].

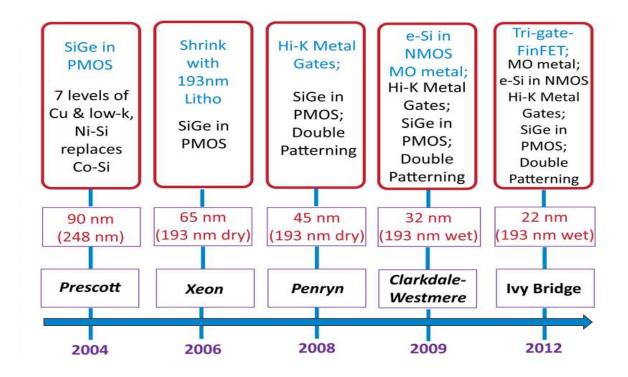

Fig. 1.3: Intel's technology roadmap for microprocessor design [8].

Fig. 1.2 shows IBM's delivery of high performing POWER microprocessors enabling multi-thread core, bigger on and off-chip cache and higher IO bandwidth [7]. Similarly, Fig. 1.3 shows the technology roadmap for Intel enabling high performing process technology which allows to pack billions of transistors on a single die within reasonable power envelop [8]. To support the ever-increasing demand for delivering high performance microprocessor in 2-3 years within a reasonable power and cost envelope, industry leaders are moving towards mostly automated synthesizable design with multi-clock and multi-power design methodology. In the current state-of-the-art design methodology for microprocessor, macros (generally within same power or clock domain) are built, timed and integrated at higher level of design hierarchy, called unit, to make the design constraints. However, these macro boundaries can be collapsed and turn-around-time (TAT) of current synthesis methodology can be improved even further for better physical design efficiency, sharing of unused slack and better logic optimization in multi-power and multi-clock domain.

In this dissertation, a <u>Multi-Million Logic Gate Synthesis</u> (MMLGS) design methodology is presented. The proposed design methodology differs from the methodologies used in the existing designs with four distinctive features:

- it allows to build a macro that is 2-3 times bigger in transistor count than what is currently done in the industry by using techniques such as soft-hierarchy, multi-VT insertion, interior pin and preplacing critical logic gates,

- it saves around 50% physical design resources (engineering man-month) due to higher degree of automation in MMLGS, otherwise traditional flow would require more circuit design, unit timing and integration resources,

- it allows designers to share unused slack safely in multi-clock domain to close timing critical paths effectively, and

- it enables designers to place and connect logic gates to proper power supply in multi-power domain design automatically and more optimally.

The proposed design methodology explains step-by-step of the physical design flow and shows how the development cycle and custom circuit design resources can be cut down by about 50% and yet maintain the same design quality. With the proposed design flow, the timing and integration resources can be eliminated in some cases, which are needed in today's design methodology to deliver high quality routed and timing closed unit to the chip. Synthesis-based design methodology can also improve power, area and timing efficiency by looking at the logic gates and drive strength across the macro boundaries. The presented data show how localized macro congestion can be resolved by sharing routing layer resources with a unit or chip. While the synthesis-based design methodology for MMLGS is proposed in this dissertation, it is also shown how techniques such as pre-routing, pre-placement, and a "soft hierarchy" (SH) can be used as aids to resolve critical timing and routing issues that are most often encountered [10].

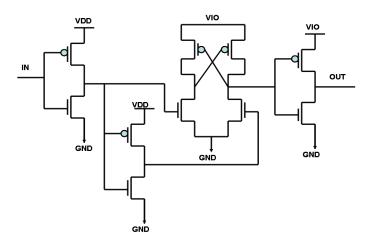

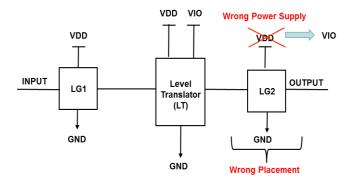

Similarly, out-of-phase clock and multi-voltage are two major requirements as more and more functions are bundled on the chip to deliver high performing circuits within a reasonable power envelope. In high speed microprocessor design, multi-clock, multi-voltage usages, and slack sharing methodologies are very common in custom circuit design areas, but in automated synthesis design flow, these methodologies need to be analyzed, understood, and implemented in such a way that backend toolsets understand timing and implementation checks. Designers generally apply the tricks of stealing time from the next cycle if there is available slack. However, sharing slacks cannot be done between out-of-phase clocks because the likelihood of

metastability increases at synchronous and asynchronous boundaries, and can cause an unstable state in circuits. Similarly, signals crossing from one voltage domain to another must be interfaced through the level shifter buffer which appropriately shifts the signal levels. Design of a suitable level shifter is a challenging job. Application of multi-voltage can be classified as: 1) Static Voltage Scaling, 2) Multi-level Voltage Scaling, 3) Dynamic Voltage and Frequency Scaling, and 4) Adaptive Voltage Scaling. These requirements of multi-voltage should be taken into consideration during physical implementation of the electronic circuits. Recent trends in physical design methodology show a big shift toward MMLGS for design productivity and time to market. MMLGS design most often requires embedded IP or custom components, such as arrays, inside the macros that may require different supply rail or sync-async interfaces [11].

In this dissertation, timing algorithm and synthesis methodology for MMLGS have been developed and proposed for sync-async interface logic, allowing cycle stealing across all hierarchies of the chip design. Also, design interfaces for multi-voltage have been analyzed and methodologies have been proposed to support the algorithms in automated MMLGS design flow. The proposed design methodology provides new paths for closing timing while shortening the design time. Developed synthesis and timing flow allow designers to share unused slack safely in multi-clock domain and automatically place and connect logic gates to the proper power supply in multi-power domain design. Compared to the baseline experiment, the experimental results show that physical design development costs can be cut by about 50% using the developed design flow.

# **Chapter 2**

# **Overview of Existing Synthesis Methodology**

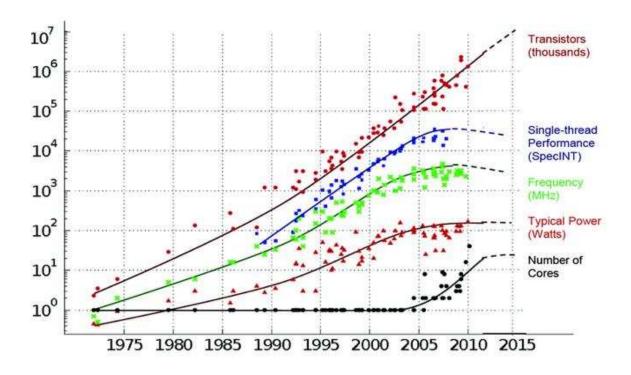

The technology market demands faster turnaround of IC design, and designers struggle to meet performance requirements as shown in Fig. 2.1. The microprocessor design industry has seen increasing costs for the design, validation, and time to market for the last decade. Past generations of microprocessors had more custom circuit design to meet the tighter cycle time battles. However, to meet the demand for shorter turnaround time, synthesizable design methodologies are preferred in most cases, sacrificing the desired speed of the chip in favor of new functionality and time to market.

Fig. 2.1: Microprocessor trend data for 35 years [12].

To meet the design constraints such as area, timing and power, custom macros most often need hand crafted schematics and layout design which are overwhelmingly time consuming and thus requires as high as four times development time compared to synthesis flows. In general, custom circuit and layout designer must plan every detail including the physical placement of design up front. One of the problems with custom design approach is to incorporate any late design change which may sometimes cause a rip-up off previously built and timed macro. In a full or semi-custom design flow, bug fixes and late changes in the design most often become very expensive in terms of turnaround time. Unit like level-2 cache (L2 cache) would have more than 50 physical partitions and thus require more man power to comply with late logic change requests. To overcome these limitations, current industry trend shows a big shift towards synthesis based design flow. While this dissertation is based on work done in MMLGS and its requirements to deal with sync-async and multi-voltage interface, basic synthesis flow, tool and methodology will be discussed in this chapter to lay down a good foundation for the research topic of this dissertation.

#### 2.1 Synthesis in Today's VLSI Design

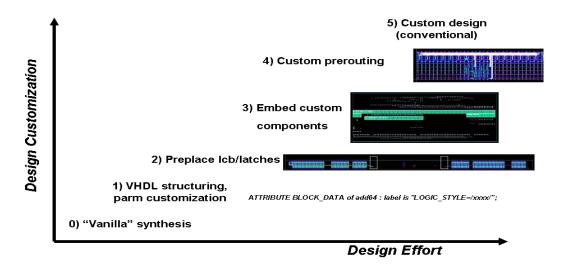

Synthesis is very popular in the ASIC world due to its low efforts and faster turnaround time. The leaders in VLSI circuit design, such as IBM, Intel, and AMD are moving towards synthesizable design at a faster pace, where most of the designs are done in ASIC methodology and synthesis tools are being used extensively. Fig. 2.2 shows the relationship between design effort and the level of customization for different circuit design styles [13] that justifies the need for synthesizable design. The major advantages of synthesis-based methodology can be summarized as follows:

• Automatic logic to schematic translation

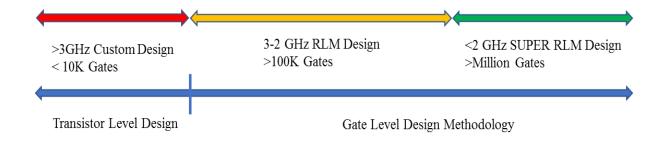

#### Introduction: Macro Design Spectrum

Fig. 2.2: Macro customization vs design effort [13].

- Reduced design cost because of faster turnaround

- Easy to incorporate last minute design change and

- No manual layout design is needed

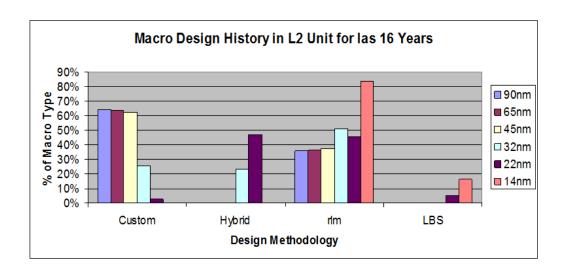

Synthesis has been widely used in the past in developing random logic macros in high latency domain. However, with recent development in EDA tools such as congestion [14-15], timing [16], and noise [17-18] aware router, a fully automated solution provides adequate results with much shorter Turn Around Time (TAT) and improved Quality of Results (QoR). Thus, more and more complex units are being designed with more synthesized macro as technology industries move from one technology to the next. Fig. 2.3 shows how macro design methodology is changing from custom to hybrid (mixed of custom and synthesis) to RLM (Random Logic Macro) to LBS (Large Block Synthesis) methodology over the last six generations of microprocessor design for an IBM's L2 cache unit [13]. As the use of automated synthesis design flows gains popularity, better understanding of tools' behavior under different input

Fig. 2.3: IBM's L2 cache macro design methodology trend [13].

constraints is crucial to successful outcomes. The final design quality of synthesized macros using modern synthesis tools can be very sensitive to inputs and design constraints given by the designers. The quality of inputs and design constraints of synthesis tool need to be carefully examined to achieve desired outcomes. Similarly, to use this synthesis tool (including timing aware placement and routing and post-processing automated tools) wisely and intelligently, designers must understand the design flow, placement of critical logic, and in some cases, wiring to solve timing and congestions of the design. Thus, before diving deep into MMLGS, basic synthesis flow is discussed in this chapter with examples and illustrations.

#### 2.2 Inputs to Synthesis Tools

To have synthesis tools to deliver intended results, it typically requires at least three user defined inputs and these are:

- HDL (Hardware Description Language) or functional logic

- Physical abstract information about the target macro, i.e. a physical bounding box

that has all the location of primary input and output of the design and routing constraints for the macro and

Timing constraints for the macro including the clock names and phase information. These constraints are often referred to as assertions.

In addition to these primary requirements, tools most often need guidance from users in the form of control files, so that they can produce timing- and routing- closed physical design with expected results. In this dissertation, IBM's synthesis tool flow called PDSRTL, Placement Driven Synthesis (PDS), has been used as an example of modern synthesis tools to analyze experimental results. Some of the methodologies of PDSRTL have been cited here as general background information.

#### 2.2.1 Register Transfer Level (RTL)

The synthesizable Register Transfer Level (RTL) description, often in either Verilog or VHDL hardware description language [19], can be optimized with respect to various constraints, including timing and/or area, using a synthesis tool, where a technology library file is being used to specify the components to be used by design. The RTL can contain parts of the design that are purely combinational or sequential, such as latches and flip-flops. In many cases, top-level RTL calls another component of the design as soft copy (i.e. another piece of logic) or hard copy (components that are built and timed separately) of some functions. Fig. 2.4 shows an example of high-level function. It is the task of physical design tools (synthesis or custom design) to translate these functions into transistor level for building the chip. Physical design engineers spend good amount of time to study the RTL to determine the data flow of the design and plan up-front to place the logic gates, metal usages and routing strategy of the design.

Fig. 2.4: An example of high level function.

#### 2.2.2 Assertions

To guide the synthesis tools to close timing at input/output interface paths at macro boundary, timing and loading requirements are needed so that EDA tool work hard to meet the design constraints. Assertions, in terms of arrival time at input with correct timing phase (arrival time relative to functional clock), expected time of arrival at output relative to functional clocks and loading at macro output, are three minimum inputs to the synthesis tool. In today's high speed design, there might be many functional clock signals operating at different speed relative to each other and they are defined as phase. In synthesis, the assertion requirements are defined a bit more in details as follows:

Primary Input (PIS): To optimize the timing and gate placement, synthesis tools need to know the data arrival time (late and early mode to cover both slow and fast design corner), functional phase tag (data arrival time with respect to the functional clock) along with the slew (rise/fall time) of the primary inputs, so that design constraints are met during synthesis

optimization. The PIS file is generally a space separated constraint file, which is being used as an input during the synthesis flow. An example of PIS can be shown in table format in Table 2.1.

Primary Output Load (POS): The macro output requirements, in terms of arrival time at the output, slew (or rise/fall time) and capacitive load to drive, are required so that the timing and electrical requirements are met at higher level of the design hierarchy. POS value is given in terms of best and worst case capacitive load so that macro is designed to meet the timing for wide range of process corners. Similarly, POS value is also given in both lumped and effective load so that macro is designed to drive a wide range of load to drive at the next hierarchy of the design. The POS file is generally a space separated constraint file, which is being used as an input to the automated tools during the synthesis flow. An example of POS can be shown in table format in Table 2.2.

Table 2.1: Example of PIS assertions.

| Input<br>Pin<br>Name | Phase | Late<br>Arrival<br>Time (rise) | Late<br>Arrival<br>Time (fall) | Slew (rise) | Slew<br>(fall) | Early<br>Arrival<br>Time<br>(rise) | Early<br>arrival<br>time<br>(fall) | Slew (rise) | Slew (fall) |

|----------------------|-------|--------------------------------|--------------------------------|-------------|----------------|------------------------------------|------------------------------------|-------------|-------------|

| nclk                 | M-    | 125                            | 0                              | 50          | 50             | 125                                | 0                                  | 50          | 50          |

| data                 | M@L   | 100                            | 100                            | 80          | 80             | 80                                 | 80                                 | 60          | 60          |

Table 2.2: Example of POS assertions.

| Output Pin | Worst Case | Best Case  | Fan Out | Worst Case     | Best Case      |

|------------|------------|------------|---------|----------------|----------------|

| Name       | Total Load | Total Load |         | Effective Load | Effective Load |

|            | (ff)       | (ff)       |         | (ff)           | (ff)           |

|            |            |            |         |                |                |

| Reload_Bus | 200        | 100        | 1       | 150            | 80             |

|            |            |            |         |                |                |

| abist_en   | 150        | 80         | 1       | 100            | 60             |

| _          |            |            |         |                |                |

Table 2.3: Example ETA assertions.

| Input Pin<br>Name | Phase | Late arrival<br>Time (Rise) |     | Early Arrival<br>Time (Rise) | Early Arrival<br>Time (Late) |

|-------------------|-------|-----------------------------|-----|------------------------------|------------------------------|

| rd_data(0)        | M@L   | 200                         | 205 | 150                          | 150                          |

| scan_out          | S@L   | 400                         | 410 | 200                          | 200                          |

**Expected Time of Arrival (ETA):** The ETA file is generally a space separated constraint file, which is being used as an input during the synthesis flow. An example of ETA can be shown in table format in Table 2.3. ETA consists of expected arrival time at the macro output (with respect to clock) along with clock phase information. Like PIS, ETA values are also given in terms of early and late arrival time of the signals so that macro is designed to function in both slow and fast corner of the process.

In addition to PIS, POS and ETA, synthesis engines can be guided for better results with additional information such as phase adjust and loading override files, where designers can override with updated phase information and input capacitance seen by tool for multi fan-in input of the design.

#### 2.2.3 Macro Physical Abstract

Another necessary input to the synthesis tools is the macro bounding box with primary input/output (PI/PO), PIN locations, and metal blockages information. Synthesis tools read the physical placement of the macro PI/PO from the macro abstract and optimize the gate placement with proper drive strength as per the loading in POS file and at the same time, meeting the expected timing as defined in ETA file. When it comes to route the macro, router uses available routing resources as defined in the bounding box or abstract of the macro.

#### 2.2.4 Control Files

Control file(s) might be thought of as additional help to synthesis but not mandatory. This control file(s) are called during the synthesis optimization process. However, for meeting the timing and quality of routings of any wires and placement of logical gates, these parameters should be considered as semi-requirements for the synthesis tools. For example:

- If the design is dominated by embedded IP, then synthesis will need IP placement information and timing rule to meet the timing and routing requirements.

- If the design is highly timing critical, the tool will need some guidance as how to use upgraded wires or use better VT (Threshold Voltage) gates to meet timing.

- If the design has a congestion problem, the tool will need to know how to spread logic to mitigate the wiring congestions.

- If certain portions of the logic needed to stay together, synthesis tool can be a guide as how to place the relevant logic gates together and so on.

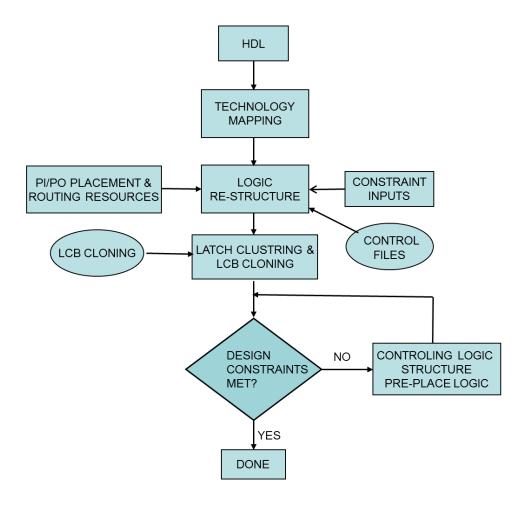

#### 2.3 Typical Synthesis Flow

Synthesis tools compile RTL design using two main phases: 1) Technology independent phase where the design is read in and simplified in combinational logic and 2) technology mapping where the design is mapped to available logic gates in a given physical library. However, before that there are few sub-steps such as optimizing clock logic and logic restructuring in the flow. In merging clock logic step, synthesis collapses incoming clock logic into one Local Clock Buffer (LCB) per clock domain. Once latch placements are done, to make wiring and timing requirements for the design, appropriate LCBs are connected for each clock

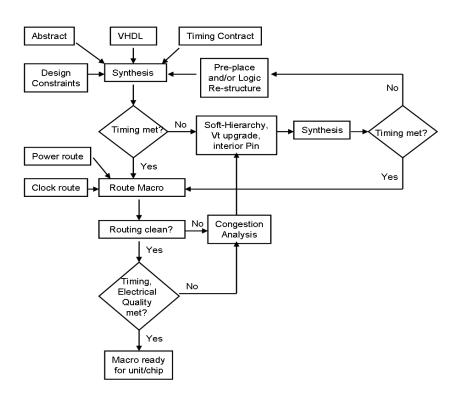

Fig. 2.5: A typical synthesis flow.

domain. LCB creates clock nets for master-slave and scan clock of the latches from mesh clock and other clock control signals as defined by methodology of each project. While inputs to synthesis are given, as discussed in previous sections, tools process this information in several steps to find an optimal solution for a given design. A typical synthesis flow is shown in Fig. 2.5. The flow contains many iterative steps and loops to satisfy the design constraints and timing requirements of a design. These steps include:

- Technology mapping

- Logic re-structuring

- Latch clustering and LCB cloning

- Controlling logic structure

- Pre-placing logic

#### 2.3.1 Logic Re-structuring

Logic restructuring involves the following activities in synthesis:

- Optimizations are done on technology-independent netlist of the design

- Wire load is assumed to be zero

- Restructure logic to decrease network interconnections, circuit area, and remove logic redundancies and

- Algorithm used to minimize logic

Some examples of logic transformation and restructuring during synthesis have been discussed as here:

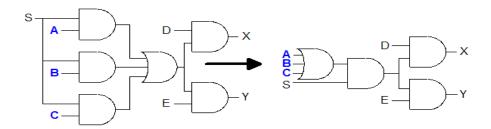

**a) Transduction:** Replace functions with more efficient ones. In the following example, Fig. 2.6.1, logic can be rearranged so that the delay is optimized. As oppose to connect signal "S" to the first level of gates, it can be forwarded to the second level by keeping same functionality to meet the timing.

Fig. 2.6.1: Logic transduction (Source: EDA, IBM).

**b) Cube Factoring:** Extract a common gate from several gates as shown in Fig. 2.6.2, where a common function for input "C" and "D" is determined and then fed into the subsequent logic.

Fig. 2.6.2: Logic cube factoring (Source: EDA, IBM).

c) Create common factors: Creating common factor, Fig. 2.6.3, and then feed it to rest of the logic helps closing timing.

Fig. 2.6.3: Common factoring (Source: EDA, IBM).

Fig. 2.6.4: Logic merging (Source: EDA, IBM).

d) Merging logic: Sometimes merging logic gates helps closing timing. It also depends on how critical is the timing for the input(s). In Fig. 2.6.4 both NAND2 gates can be merged to create NAND3 to improve the overall timing. However, if signal "C" is critical, this type of merging will hurt the timing on "C" because NAND3 is a slower logic-gate than NAND2.

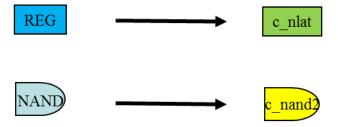

### 2.3.2 Technology Mapping

Given a technology independent structural description, a target technology, and a set of design constraints, technology mapping is the process of implementing the structural descriptions in the physical domain at the same level of abstraction, where all design constraints are fulfilled. In this step of synthesis, logic gates are mapped to a specified design technology library for the project. For example: "REG" is defined as state storing element "latch" in RTL, however, during this step, tool will look for equivalent functional logic gates such as "nlat", "eslat" etc. in the adopted project. During the technology independent phase of synthesis, the Boolean equations representing the logic network are subject to logic optimization for minimizing the number of literals, which have been shown to correlate well with total cell area [20]. Fig. 2.7 gives an example how physical library is mapped to technology independent physical library gates. Optimal gate placement is a crucial part in synthesis. A timing aware placement and optimization algorithm has the following steps:

Fig. 2.7: Technology mapping.

- a) Initial Placement: Based on the Steiner modeling of the net [21], synthesis use placement algorithm for initial placement of the logic gates. This step is basically based on the wire length between the logic gates. Once initial placement is done, synthesis can be guided with some parameter for a targeted logic-gate-placement-density in certain area of the design. Similarly, if the design is very congested, a set of parameter can be used to spread out the logic gates. To avoid the high pin density of certain gates, synthesis parameter could be very handy to avoid local congestions. Global placement is one of the most important steps in a physical synthesis flow. The last few years have witnessed a renaissance in the research on wire length-driven global placement, largely due to the availability of challenging benchmarks derived from real industrial design [22-23].

- b) Placement Optimization: Placement-aware synthesis attempts to use a placement tool [24-25] to perform a partial physical design to compute more accurate interconnect loading estimates on a net-by-net basis. After the initial placement, synthesis algorithms go through several iterations of the placement to optimize the timing. In this phase, the tool determines which gate-movement would result in the most benefit to resolve timing violations. In Fig. 2.8, the dotted box is a new placement of the gate that is driving three blue boxes on the right, yielding minimum movement to solve the timing pressure.

There are several parameters being used in synthesis in order to meet timing and improve the routability of a given design. Here are some examples of most frequently used parameters, which can be used to guide placement of the logic gates:

- target\_density: Controls the density of gate placement to avoid congestion.

- place\_xfactor: Spread out complex logic gates to avoid congestion.

Fig. 2.8: Gate placement optimization.

• blockage\_file: Specify areas where gate placement is not allowed.

Traditionally, optimizing the wire length has been the key objective during global placement, with routability being addressed via post-placement refinement techniques. There have been attempts to alleviate congestion via routability-driven global placement, but they rely on rudimentary, and most often, inaccurate techniques like pin-density or probabilistic congestion estimation [27-30].

In initial placement optimization, netweights (assign number to a net to define criticality) and attractions (define which gates should be closed to each other) may be applied and are not meant to be extensive. At this time, no placement legalization is performed to save run time. Placement optimization is done with netweights and attraction based on the timing of the nets. Examples of netweights and attractions concepts are shown in Fig. 2.9. Nets with higher weight will be given higher priority to place the associated gates closer to the source gate to close the timing for critical nets. There are several options for attraction method that can be used in

Fig. 2.9: Slack optimization.

synthesis to solve the timing failure. For example, synthesis can find out the worst slack for a sink gate and can apply attraction to the instance name or pin name of the sink. Similarly, net weight can be used on PI/PO of a gate to place them close to each other. User can control these placements by using a parameter in run directory. Examples:

net\_weight\_file - Can be used to give user-driven net weight file to place gates closerattractions\_file - Can be used to specify user-driven attractions file

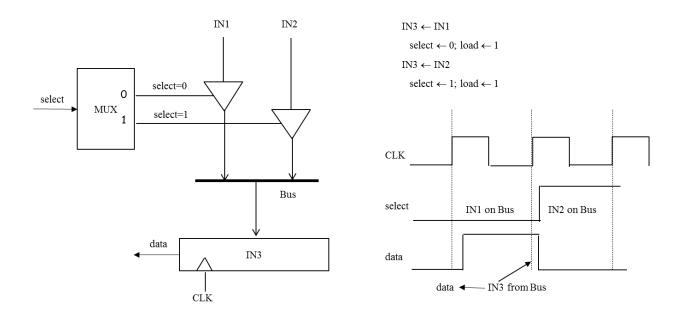

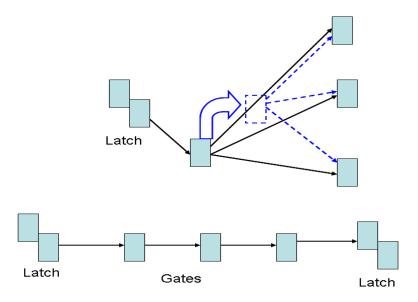

c) Latch and LCB Placement: Local Clock Buffer (LCB) is used to create master-slave and scan clocking for the latches, where LCB is connected to a main mesh clock, along with other clock control signals. These control signals are being used to either shape-up clock pulse or mode of operation. In any design, it is common that latches could be driven by multiple clock domains and clock gating functions. And thus, synthesis must acknowledge physically aware clustering of latches and clock domains, where, latches cluster around the driving LCB to meet

Fig. 2.10: Latch and LCB placement flow.

the tight clock skew guidelines of the projects. However, the placements of these latches and LCBs are very iterative placement process. Clock placement and routing optimization steps can be pictured in Fig. 2.10.

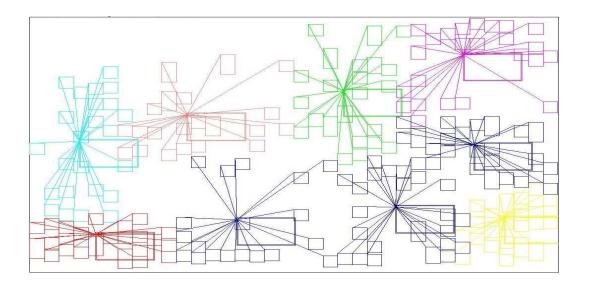

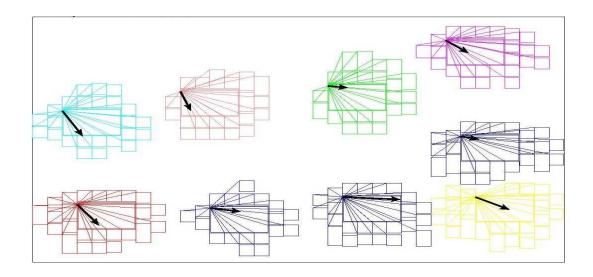

The latch and LCB placement algorithm starts with one LCB per clock domain, followed by cloning and power-up of LCBs with optimal latch connection to meet clock loading, delay and other design spec. An example of LCB and latch placement with several clock-gating domains is shown in the following picture, Fig. 2.11, where each color represents a different clock domain. Once synthesis goes through the initial LCB placement, latch clustering, LCB legalization and final clock placement, the above design ends-up looking like what is shown in Fig. 2.12.

Fig. 2.11: Initial latch and LCB placement (Source: EDA, IBM).

Fig. 2.12: Final latch and LCB placement (Source: EDA, IBM).

- d) Design Violation Clean Up: At this stage, PDS will look at the connectivity and correct any design violation. These violations typically involve gate topologies, fan-in/fan-out restrictions, restriction on latch-input and LCB, etc., defined by the methodology of the project. For example: 1) Driver to the latch input cannot be driven by illegal gates, 2) Driver to the latch input cannot have more than one sink i.e. only sink is latch and 3) Macro output cannot have a feedback loop i.e. cannot have internal logic to drive. At the end of this phase of the design, the tool would re-do netweights and attraction steps to incorporate additional logic to place.

- e) Final Placement: At this step, all the critical pieces of logic are very much locked-up. These logic gates include LCB, Latches, driving gates of latches etc. Similarly, as explained in the previous section, net-weight/attractions are also locked down. At this point and forward, physical placement refinement is done to make timing and power spec of the design. Refinement will perform physically aware optimizations but will not drastically change the placement solution. Part of this refinement is to correct electrical and timing corrections. The tool would

swap a gate with bigger gates and all sub-sequent gates to fix the slew or slack violation. Similarly, slower gates will be replaced by faster gates to meet the timing. The starting point of this stage is a placed netlist with a clocking solution locked down. In short, refinement will perform physically aware optimizations but will not drastically change the placement solution, i.e., minor moves/legalizations will occur.

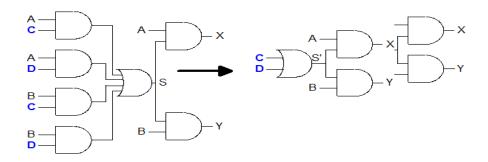

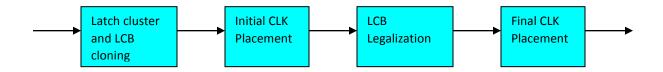

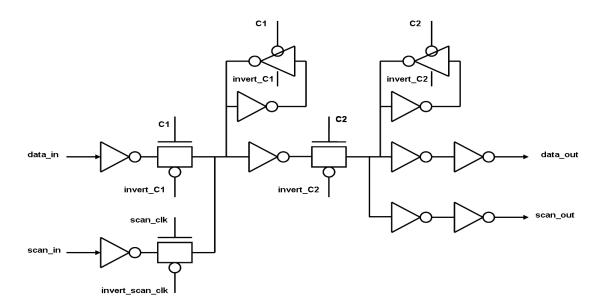

# 2.3.3 Latch Clustering and LCB Cloning

To meet the timing, loads on critical logic are separated by cloning both latch and logic gates. A sample of such cloning is illustrated in the following example, where latches are coded to drive different output logic, when input is the same for both latches. However, synthesis tools need to be enabled with parameter so that PDS can clone latches, and similarly, equivalent latches must be defined in VHDL (or Verilog) before going to the synthesis process. Parameters must be enabled via synthesis parameter. A functional latch is described in details in Section 4.2 of Chapter 4. Following are the examples, Fig. 2.13, of two equivalent latches (cloned) in the VHDL, where one input net is connected to both latches but those latches are driving different outputs.

pds\_use\_cloned\_latches: true #parameter in constraint file

unit\_control: entity latches.nlat

port map (c1 =>  $master\_clk$ ,

$c2 => slave\_clk,$

$scan\_clk => scan\_clk,$

$scan_in => funcscan_in(0),$

```

=> func\_scan\_out(0),

scan_out

data_in

=> unit\_data\_in(0),

data_out

=> unit_data_out(0))

unit_control_colone: entity latches.nlat

port map

(c1

=> master\_clk,

c2

=> slave\_clk,

scan_clk

=> scan_clk,

=> func\_scan\_out(0),

scan_in

=> func_scan_out(1),

scan_out

data_in

=> unit\_data\_in(0),

=> unit\ data\ out(1),

data out

)

```

Fig. 2.13: Latch clustering and LCB cloning.

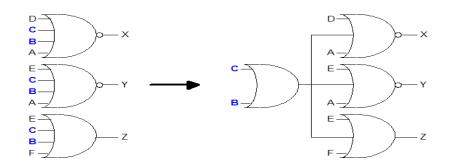

### 2.3.4 Control Logic Structure

To control synthesis flow, sometimes designers can hard code the logic gates with appropriate logic style and drive-strength with some attributes in VHDL. There are some advantages and disadvantages for such coding because in the event of hard coding, synthesis will not optimize gates to meet the slew/slack requirements of the design. Similarly, poor coding or lack of understanding of the optimization can cause sub-optimal design. This coding is used as a

hint to the tool, not a requirement. Designers could use "Logic Style Direct" or "No modification" in VHDL source. Here are some examples of VHDL Logic Style Direct & NO\_MODIFICATION.

ATTRIBUTE BLOCK\_DATA of example\_dir\_mod0: label IS "LOGIC\_STYLE=/DIRECT/";

ATTRIBUTE NO\_MODIFICATION of example\_dir\_mod0: signal IS "TRUE";

stall\_blk1a0: example\_dir\_mod0 <= NOT (main\_eec OR main\_stall);</pre>

stall\_blk1b0: example\_dir\_mod1 <= NOT (main\_stall OR ecc\_data);</pre>

Like "Logic Style Direct" or "No\_modification", synthesis understand the "structure preserving logic" initiated by the designers. Advantage of structure preserve is: consistent logic and synthesis determine the drive strength. However, the designers need to include realistic logic in the design. Designers can also preserve the output drivers as coded in VHDL. The following is an example, Fig. 2.14, of how to hardcode a NAND gate in VHDL with desired drive. These gates belong to synthesis physical design library.

use\_cw\_nand2\_rd0\_l: entity stdcell.cw\_nand2

Fig. 2.14: Logic structure control.

### 2.3.5 Pre-Placing Logic

Synthesis does very good job working on complex, Boolean equations of non-structured control type logic macro. To save area and close timing, sometimes synthesis needs "hand holding" i.e. placement information, for the timing critical and data flow oriented logic. In addition to hard IP and custom components, synthesis most often needs placement and logic topology information for critical logic, such as encoder, decoder, mux select etc. to converge to the desired solution. This pre-placement is generally a one-time job that requires understanding of the data flow of the unit. A sample of placement file that is being called during synthesis is given in following example:

begin\_place

place <inst\_name> xloc yloc <rot> movetype=fixed

end\_place

where, <inst\_name>: name of instance in VHDL;

*xloc, yloc: x-coordinate, y-coordinate of the instance in floor-plan;*

<rot>: rotation of the instance in floor-plan;

movetype: instance can be moved in synthesis or not.

# 2.4 Review of Quality of Data

There is a common saying in the synthesis world: "Garbage in, garbage out". Synthesis engines heavily depends on the quality of the inputs that it gets and optimizes logic structure, and places them to close timing. Otherwise, optimization tools will spend time unnecessarily. These essential inputs for synthesis tools are discussed here. Good quality assertions with PIS, POS and

ETA are essential otherwise synthesis will work on the wrong paths. Synthesis has a direct impact on the quality of the logic that is entered. If the slack is really negative, either assertions are way off, or the logic still needs major work. Designers should not have too much logic between latches or make sure that not too much logic fighting for the same physical area or IOs are not congested to access. Otherwise, this may lead to local congestion.

Macro pin placement should be done from unit prospective to avoid extra timing penalty and congestion. Also, input pins feeding a critical cone should be placed together, so that extra buffering is avoided. Duplication of PINs should be considered for large fanout nets. Similarly, PO pins fed by common critical cone(s) should have close placement. Sometimes designers can use macro internal pins instead of edge-pin so that unit can use better performing wires to connect input and output of the logic gates.

### 2.5 Synthesis Output

Each step of synthesis produces a different type of output based on the tool that is being used. In this dissertation, experiments are done in IBM's tool flow and thus some of the steps are discussed as follows:

**Technology Mapped Netlist:** The first step that produces technology mapped netlist from RTL. At this step, no optimization and no placement is done. The tool basically maps logical gates into available physical design gates in the library as discussed in Section 2.3.2.

**Initial Optimization:** At this step, the tool still has a technology-mapped netlist with very little placement and some optimization. This optimization is based on wire length and placement of gates. Buffer re-powering, removal, and re-placing are done at this step. Net weight and attraction are being done.

**Final Optimization:** This placement is after clock-optimization and has very little change in placement of the gates. Timing, electrical and power optimizations are done at this stage. Legalization of placement is done in Final Optimization.

**Refine Steps:** It is the last step in synthesis and the tool tries to deliver optimized design with the least electrical violation and optimized power. Major optimizations include:

- Electrical violation correction

- Efficient fanout trees

- Repowering, buffering, logic restructuring, pin swapping, cloning etc.

- Vt recovery (Remove leaky gates for better power design)

### 2.5.1 Major Output Files

**Log Files:** This file has all the run details including errors and warnings while the job runs. This is a very helpful file to debug any problem that may occur during synthesis steps.

**History:** This file keep track of summary of data for all runs in same directory. These data include: #of latches/LCB, macro utilization (logic gate density in macro), latch to latch slacks, run time, type of gate (logic gates with different kind of threshold voltage for leakage power) usages, CPU usages, total logic gate width in the design etc.

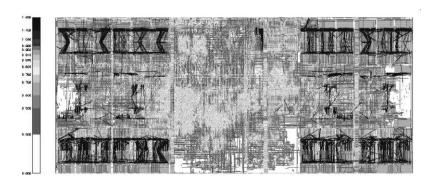

**Plots:** A routing and timing closed macro is the end goal for the designers. The provision of writing out the macro's internal logic gate and IP placement, vertical and horizontal wiring congestion, slack distributions are plotted for designers to give an overall picture of the design. Based on the plots, designers can make improvements to the quality of the design by mitigating noise and timing violations of the design using available methodology in synthesis.

Fig. 2.15: Example of worse slack plot in synthesis.

Distributions of Gate Array (GA) cell: GA cells are used to fix bugs when rest of the design is frozen. In synthesis, these information is written out as plots and thus gives a good pictorial view to designers so that designers could take a look and decide which gates to use to fix functional and timing bugs. An example of such a plot, worst slack, is presented here in Fig. 2.15, where the source and sink latch are colored in blue and green respectively. Designer can look at the placement of these part of the logic and consider several options, as discussed in Section 2.3 to close timing on this macro.

**Timing Reports:** Tool writes out several timing reports (also known as endpoint report) for user to look at. These includes as follows:

- Comprehensive timing report: This comprehensive timing file consists of timing information on all nets and gates in the design for all timing phases.

- Endpoint Report: This output file of synthesis is shorter and user friendly version of comprehensive report. It includes both latch to latch and primary input/output paths containing the delay information for the gates and wires on the paths.

Latch to Latch Endpoint Report: Out of all files that synthesis writes out, this file is the most useful to the designers. It allows designer to focus on macro internal latch to latch paths while the PI/PO paths are still in flux at the primary stage of the project. Matter of fact it is very typical that at the early stage of project, designer would relax the PI/PO paths so that internal paths get higher attention to fix the timing violations. Similarly, designers also look at another latch to latch endpoint file with "zero wire length" where there is no wire delay in the design and thus one can quickly determine whether this logic paths can be closed in synthesis or not or need logic fixes. An example of Endpoint file is shown in Fig. 2.16, where gate, wire delay and rise/fall time is broken down per logic gate.

| Phase     | Rise/    | Slack  | Delay  | Arr. Time | Slew  | Load  | Sink  |

|-----------|----------|--------|--------|-----------|-------|-------|-------|

| Name      | Fall(ps) | (ps)   | (ps)   | (ps)      | (ps)  | (ff)  | Gate  |

| Setup MA- | F        | 250.00 | 0.00   | 47.00     | 0.00  |       | LCB   |

| MA@L      | R        | 79.89  | 32.15  | 210.70    | 48.05 | 1.39  | LATCH |

| MA@L      | R        | 79.89  | 6.07W  | 204.63    | 46.54 | 2.00  | INV   |

| MA@L      | F        | 79.89  | 22.85  | 181.78    | 11.68 | 0.80  | INV   |

| MA@L      | F        | 79.89  | 0.27W  | 181.51    | 11.58 | 1.92  | NAND2 |

| MA@L      | R        | 79.89  | 9.60   | 171.91    | 17.58 | 0.80  | NAND2 |

| MA@L      | R        | 79.89  | 0.05W  | 171.86    | 17.56 | 0.88  | XOR2  |

| MA@L      | F        | 79.89  | 15.11  | 156.75    | 21.72 | 5.93  | XOR2  |

| MA@L      | F        | 79.89  | 3.29W  | 153.46    | 19.68 | 17.62 | INV   |

| MA@L      | R        | 79.89  | 12.54  | 140.92    | 27.29 | 3.87  | INV   |

| MA@L      | R        | 79.89  | 6.83W  | 134.10    | 22.65 | 10.37 | NAND2 |

| MA@L      | F        | 79.89  | 12.23  | 121.87    | 19.36 | 2.33  | NAND2 |

| MA@L      | F        | 79.89  | 0.19W  | 121.68    | 19.31 | 2.54  | NOR2  |

| MA@L      | F        | 79.89  | 29.40  | 92.28     | 56.12 | 0.45  | NOR2  |

| MA@L      | F        | 79.89  | 23.34W | 68.93     | 24.62 | 40.07 | INV   |

| MA@L      | R        | 79.89  | 12.08  | 56.85     | 28.20 | 5.40  | INV   |

| MA@L      | R        | 79.89  | 0.84W  | 56.02     | 27.99 | 5.99  | NAND2 |

| MA@L      | F        | 79.89  | 15.37  | 40.65     | 11.55 | 1.00  | NAND2 |

| MA@L      | F        | 79.89  | 0.05W  | 40.59     | 11.52 | 1.08  | LAT   |

| MA-       | F        | 40.59  | 0.00   | 47.00     | 0.00  |       | LAT   |

Slack: Cycle Time + LCB delay – path Delay = 250 + 40.59 - 210 = 79.89ps

Fig. 2.16: Example of timing path in synthesis.

**Netlist:** It is the ultimate output from the synthesis tool that has all connectivity, placement and mapped to available physical gates of the physical design library. This text based netlist file is converted to layout cells once imported into cadence library and at this point physical designer can open the placed gates in GUI to analyze any timing fails and possible placement in the design with some parameter or customization. Another usage of this cadence based netlist view is: designer can edit this netlist for possible logic change (ECO: Engineering Change Order) because they can visually check the placement of other gates and come-up with better solution to optimize routing, metal usages and timing for the design.

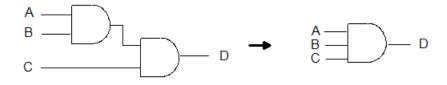

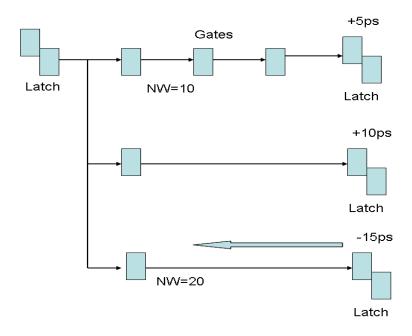

### 2.6 Early Mode Padding (EMPAD)

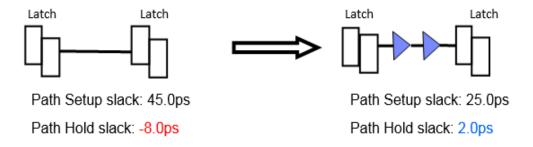

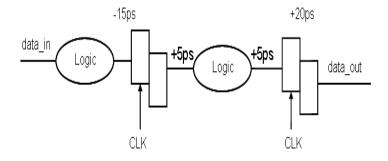

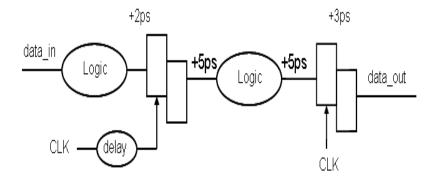

Hold timing violations are the fast path violations, and so it is important that the timing represents the fastest environment in which the chip will operate (best case voltage, temp, etc.). EMPAD is a part of placement driven synthesis where optimization is needed to fix hold timing violation in the design. Hold violation is a violation when data arrives faster than the clock at the sink latch. These are the 'must' fix in the design and involve to slow down the fast paths. In Fig. 2.17, design has back to back latches connected mostly to stage logic so that correct balance of latency exists in the design. There is not enough logic gate between the left latch packs, where the set-up and hold slacks are shown as 45.0 and -8.0ps (hold violation) respectively.

Fig. 2.17: Example of early mode padding (EMPAD).

In order to fix this hold violation, an inverter-pack (two gates with blue color) has been added on the logical path and thus the set-up and hold slacks became 25.0ps and 2.0ps, which satisfy both the late and early mode timing check for the design. Also, to fix EM failures, gates on the timing paths can be sized down to slow down the data arrival time. However, the designer(s) must be very careful in downsizing gates so that noise does not become a problem because smaller gates are more susceptible to noise. Similarly, it is also highly recommended to place EMPAD gates at the most downstream logic to minimize the usages of gates to save power and area.

### 2.7 Routing

Logic design team can avoid routing problems and achieve greater success by adopting a physical- and congestion aware synthesis methodology that reduces iterations between front- and back end tools, which positively impacts the die size and schedule time. Given the delay impact of wires in today's process geometries, modern timing-aware routers will try as much as possible to detour those routes that are non-timing critical, but this is not always possible. And given the prominence of physical wire delays in today's geometries, it is likely that a non-critical path becomes critical after its route is detoured. Further compounding the problem, physical tools tend to buffer those detoured routes in an attempt to speed them up, and this can create further congestion [31]. In the physical design stage, not only global routing, but some new placement algorithms begin to consider the congestion minimization as one of the most important objectives of optimization besides area and timing [32-38].

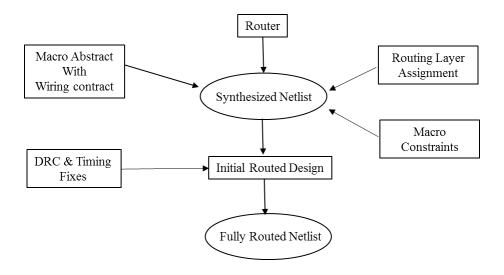

The routing tools involved in these steps are: power routing, clock routing and signal routing. However, as data prep, the router will read the synthesized data as netlist, where all the connectivity is already defined, along with macro-bounding box with wire allocation and

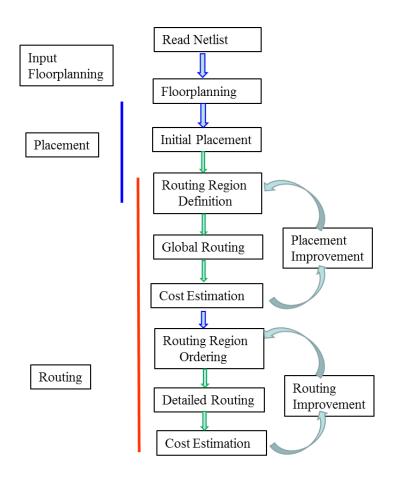

constraint files. In addition to the synthesized netlist, the router needs to know what layers of metals it can use to route the macro. Abstract of the macro has PI/PO placement information and cover cell has all blockage information that is needed during the routing steps. A constraints file is used as an aid to the router, where any specific such as a control file for power routing layers, is defined. A flow diagram for routing a synthesized macro with inputs is shown in Fig. 2.18, and sequence of the tool executions are shown in Fig. 2.19. Routing jobs in synthesis are mainly divided into two major steps: 1) Global Routing and 2) Detail Routing where following tasks are performed [39]:

### 1. Global Routing

- The logic gate placements are preserved from synthesis

- Identify routing resources to be used

- Identify layers (and tracks) to be used

- Assign particular net to these resources and

- Also, used in floor-planning and placement

### 2. Detail Routing

- The logic gate placements are preserved from synthesis

- Define pin-to-pin connections

- Must understand most or all design rules and congestion issues of the design

- May use a compactor to optimize result

- Necessary in all applications

Fig. 2.18: Input and output of routing in synthesis.

Fig. 2.19: Routing flow (Courtesy: IBM EDA).

Fig. 2.20: Routed design.

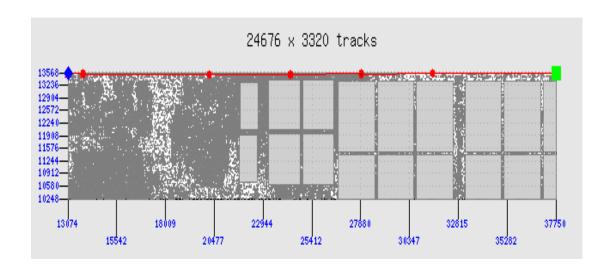

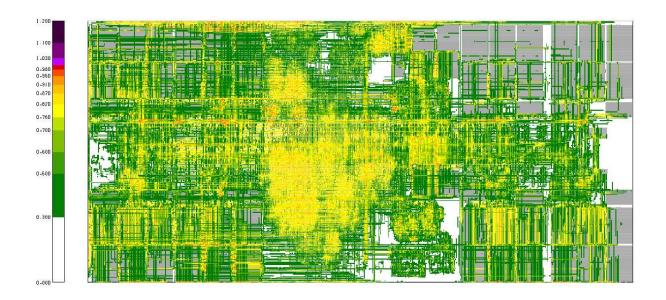

To route any design in most effective way, it is very important to look at hot spots that design may have due to the congestion. The design may get routed but in the long run designers must be careful for back-end tool fails such as noise, electromigration, electrical rule fails, and timing fails due to noise. Designers should also think about having some extra space for future changes and bug fixes. There are some home-grown tools that can be used to find out hot spots in the routing that can led to space out logic gates or allow higher layers of metals if available. In Fig. 2.20, it is shown how congested the design is by taking a picture of metal routings and coloring red where design is highly congested. Yellow indicates caution, while green indicates no substantial problem to route.

### 2.8 Post Routing Optimizations

Once design is routed, another post processing tool can be used to fix the design violation left by the router in a minimally disturbing way. One can perform the optimization after detail routing to fix a post-routing timing "jump" [40]. Some usages of these tools are discussed here:

### • Electrical Quality

- Rise/Fall time fail fix

- Max loading fix

## • Timing Quality

- Improve both late and early mode timing fails

- Improve power by replacing leaky gates with power efficient gates

- Remove unnecessary routings to fix some design rule violations

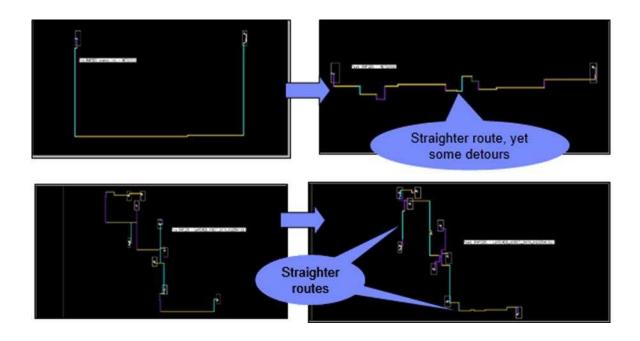

Post processing tools work on already routed designs for better optimization with incremental routings and placements to fix electrical and timing fails. However, it works on the design that is already placed and has detailed wiring done. It fixes scenic nets and tries to make it straight. Given a set of scenic nets, post-processing tool rips-up and re-routes these nets. Once rerouting is done, it is much straighter than the original routings as captured in Fig. 2.21. Table 2.4, on the other hand compares both early and late mode slacks in addition to slew and maximum cap fails before and after running the post-processing tools once the design is routed.

Table 2.4: Post processing tool to fix timing violation.

|                          | Beginning | Ending |